We are very excited to announce the alpha release of our Rocket chip generator. This generator toolkit can be used to create instances of our high-performance, energy-efficient Rocket processor suitable for both high-speed simulation and full synthesis. We have provided a collection of components that go well beyond simple pipeline RTL in order to allow you to generate a complete Rocket implementation, including a memory subsystem.

What is Rocket?

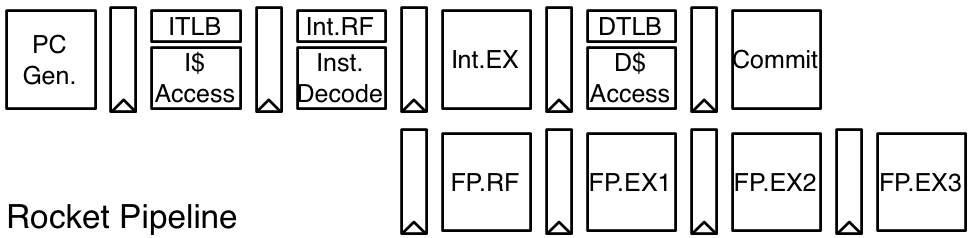

Rocket is a 5-stage single-issue in-order pipeline that executes the 64-bit scalar RISC-V ISA (see the pipeline diagram below). The scalar datapath is fully bypassed but carefully designed to minimize the impact of long clock-to-output delays of compiler-generated SRAMs in the caches. For example, we have moved the branch resolution to the M stage to reduce the critical D$ bypass path. A branch target buffer, a two-level branch predictor, and a return address stack together mitigate the increased performance impact of these control hazards. Rocket implements an MMU that supports page-based virtual memory and is able to boot modern operating systems, including Linux. Both caches are virtually indexed and physically tagged with parallel TLB lookups. The data cache is non-blocking, allowing the core to exploit memory-level parallelism.

Rocket has an optional IEEE 754-2008-compliant FPU, which can execute single- and double-precision floating-point operations, including fused multiply-add (FMA), with hardware support for subnormals and other exceptional values. The fully-pipelined double-precision FMA unit has a latency of three clock cycles.

Note: The description above is an excerpt from our ESSCIRC paper “A 45nm 1.3GHz 16.7 Double-Precision GFLOPS/W RISC-V Processor with Vector Accelerators“.

What Does the Generator Do?

The Rocket chip generator produces parameterized RTL for the Rocket core and associated caches, glues it to an uncore/memory system, and then transforms all of the above into one of the following:

- High-speed C++ simulator: The generated C++ simulator is faster than a Verilog simulator, and is also able to generate vcd waveform dumps for debugging.

- Verilog optimized for FPGA: We also released scripts to map the generated Verilog down to a ZYNQ FPGA. Please take a look at the open-sourced fpga-zynq repository.

- Verilog optimized for VLSI: We have taped out three 28nm test chips and five 45nm test chips with the Rocket chip generator. Unfortunately, we cannot open source VLSI scripts due to NDA restrictions.

Who Should Use the Generator?

People who want a RISC-V core for VLSI or FPGA implementation. If you just want it for that purpose, as is, then little work is required of you. Please note that Rocket is designed and optimized for VLSI implementations, and therefore will not result in the best FPGA resource utilization relative to a dedicated soft core design. However, it is a real processor that runs our entire software stack (including Linux and user-level applications such as cross-compiled Python).

With a little effort, you can understand the provided parameters and change them to better utilize your available HW resources. With more effort, you can learn Chisel and make changes to the design. In the future, we’ll make it easier to integrate custom accelerators.

What Are the Next Steps?

Download the Rocket chip generator from github at this link: https://github.com/ucb-bar/rocket-chip. The README addresses the specific contents of the rocket-chip repository, how to generate particular Rocket implementations, and how to parameterize a Rocket core.