**Free Chips Project:** a nonprofit for hosting opensource RISC-V implementations, tools, code

Yunsup Lee SiFive

# SiFive

## **Open Source**

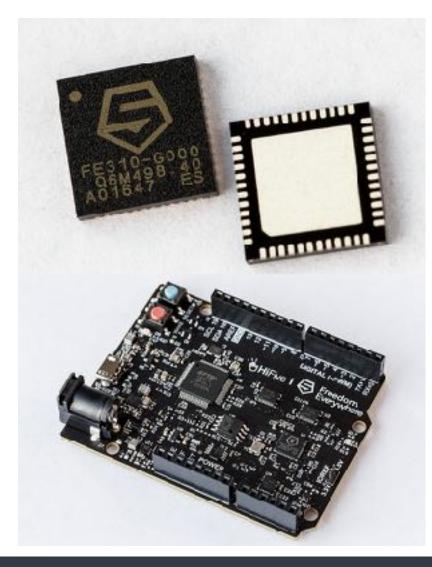

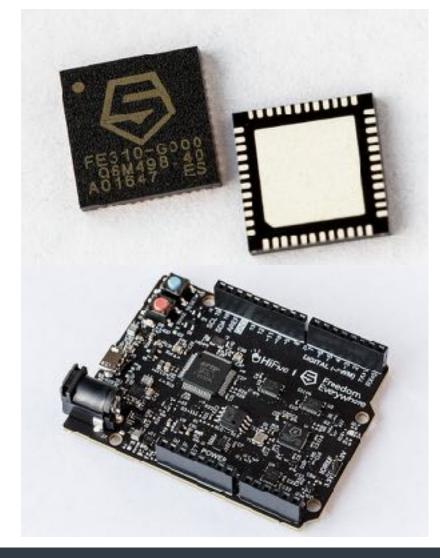

#### We Open-Sourced the Freedom E310 Chip!

ج

(#

s

## We Open-Sourced the Freedom E310 Chip!

- RTL & FPGA scripts

- <u>https://github.com/ucb-bar/rocket-chip</u>

- <u>https://github.com/sifive/sifive-blocks</u>

- <u>https://github.com/sifive/freedom</u>

- Board Support Packages (BSP)

- <u>https://github.com/sifive/freedom-e-sdk</u>

- <u>https://github.com/sifive/freedom-u-sdk</u>

- Documentation & Board Schematic

- https://dev.sifive.com

- Forums

- https://forums.sifive.com

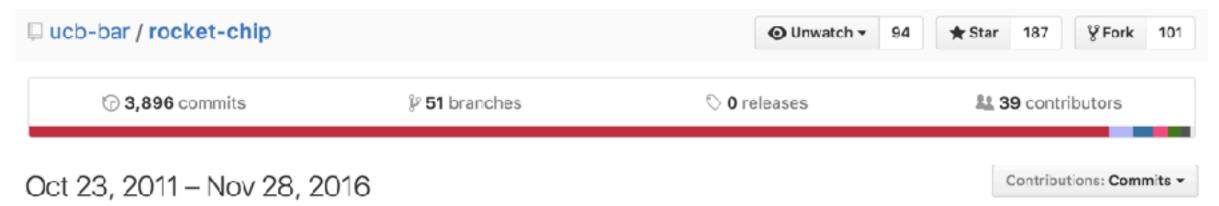

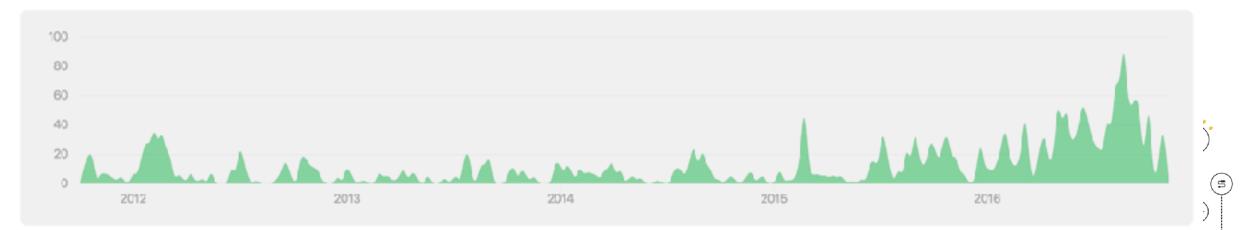

#### **Rocket-Chip Generator Repository Statistics**

https://github.com/ucb-bar/rocket-chip

📮 ucb-bar / rocket-chip

Olunwatch → 94 ★ Star 187 ¥ Fork 101

Ŷ

(#)

#### **Rocket-Chip Generator Repository Statistics**

https://github.com/ucb-bar/rocket-chip

| 📮 ucb-bar / rocket-chip |               | O Unwatch ▼         | 94 | \star Star | 187     | Ϋ́ Fork | 101 |

|-------------------------|---------------|---------------------|----|------------|---------|---------|-----|

| 🕝 <b>3,896</b> commits  | F 51 branches | 🛇 <b>0</b> releases |    | 보 3        | ibutors |         |     |

ŝ

4

#### **Rocket-Chip Generator Repository Statistics**

https://github.com/ucb-bar/rocket-chip

Contributions to master, excluding merge commits

🖨 Si Five

Our contributions are under the Apache v2 license

ŝ

÷

Our contributions are under the Apache v2 license

- Rocket Core

- Added RV32I + M/A/F support, compressed support, blocking data cache, and data SRAM options

Our contributions are under the Apache v2 license

- Rocket Core

- Added RV32I + M/A/F support, compressed support, blocking data cache, and data SRAM options

- TileLink

- Open cache-coherent interconnect with memory-mapped I/O support

Our contributions are under the Apache v2 license

- Rocket Core

- Added RV32I + M/A/F support, compressed support, blocking data cache, and data SRAM options

- TileLink

- Open cache-coherent interconnect with memory-mapped I/O support

- Diplomacy

- Global parameter negotiation framework

Our contributions are under the Apache v2 license

- Rocket Core

- Added RV32I + M/A/F support, compressed support, blocking data cache, and data SRAM options

- TileLink

- Open cache-coherent interconnect with memory-mapped I/O support

- Diplomacy

- Global parameter negotiation framework

- Other primitives

- Multi-clock support, clock crossings, and asynchronous reset flops

ສ

https://github.com/sifive/sifive-blocks

https://github.com/sifive/sifive-blocks

- Low-speed Peripherals

- SPI, UART, PWM, GPIO, PMU

- Written in Chisel with TileLink interfaces

ŝ

4

https://github.com/sifive/sifive-blocks

- Low-speed Peripherals

- SPI, UART, PWM, GPIO, PMU

- Written in Chisel with TileLink interfaces

- High-speed Xilinx FPGA Peripherals

- Wrappers for MIG DDR block and PCIe block

÷

https://github.com/sifive/sifive-blocks

- Low-speed Peripherals

- SPI, UART, PWM, GPIO, PMU

- Written in Chisel with TileLink interfaces

- High-speed Xilinx FPGA Peripherals

- Wrappers for MIG DDR block and PCIe block

- Our vision to make a plug-and-play SoC generator starts with these reusable building blocks

https://github.com/sifive/freedom

SiFive

https://github.com/sifive/freedom

• Submodules both rocket-chip and sifive-blocks

<u>َ</u>جَ

(#)

s

https://github.com/sifive/freedom

- Submodules both rocket-chip and sifive-blocks

- Top-Level SoC Integration

- Serves as a good baseline to build an SoC with your own custom blocks

https://github.com/sifive/freedom

- Submodules both rocket-chip and sifive-blocks

- Top-Level SoC Integration

- Serves as a good baseline to build an SoC with your own custom blocks

- FPGA scripts are also open-sourced

- Freedom E300 Arty FPGA Dev Kit

- Freedom U500 VC707 FPGA Dev Kit

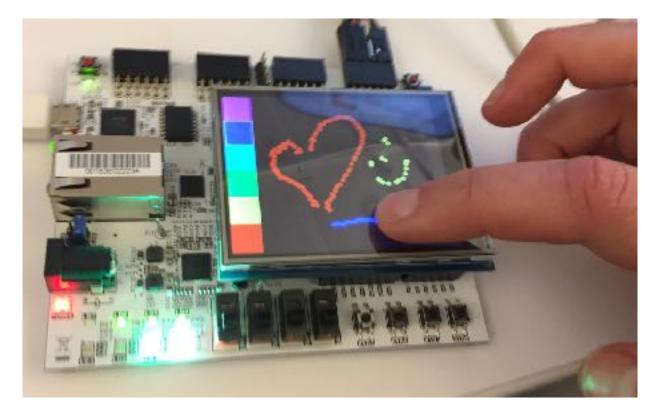

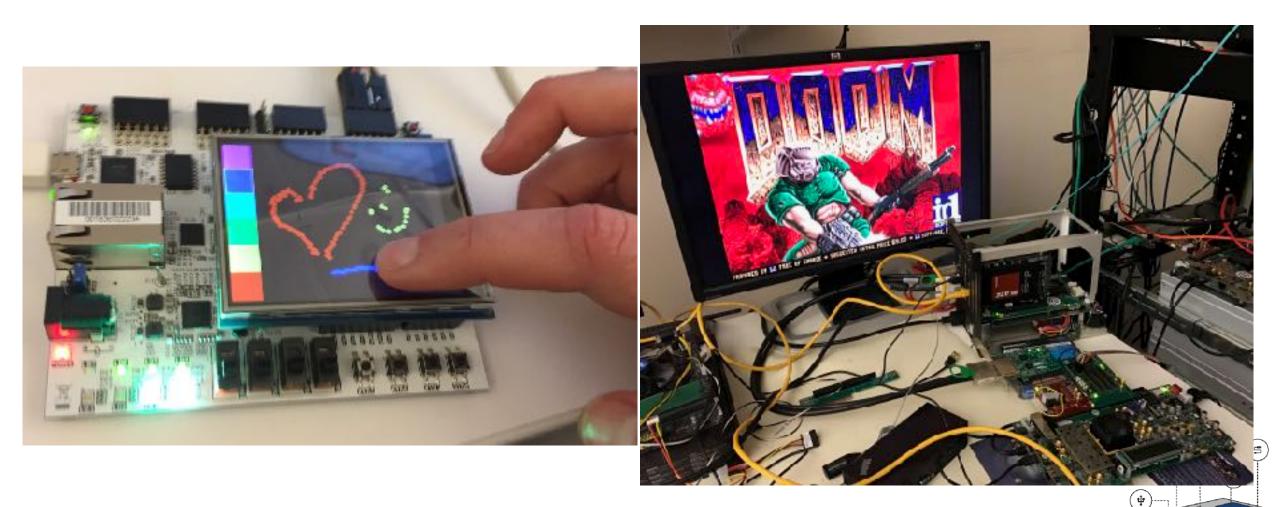

#### Freedom FPGA Dev Kits

Start prototyping your innovative ideas on Freedom platforms!

ج

(#

(s)

#### Freedom FPGA Dev Kits

Start prototyping your innovative ideas on Freedom platforms!

## But, it takes a village to make open-source hardware real

## Launching the "Free Chips Project"

Non-Profit "Home" for Open-Source Codebase

- Mission: Home for Open-Source Codebase to Enable Faster, Better, Cheaper Chips

- Initial contributions from SiFive and Berkeley

- Call for participation!

- Any questions?

Sustain and evolve open-source software tools and HDL code for system-on-chip (SoC) design

Ensure free and open contributions are available to all of the SoC design community

Manage publicly accessible, online repositories of source code, documentation and issues