#### **Power Matters.**<sup>TM</sup>

# Mi-V RISC-V Ecosystem

## **Agenda**

- RISC-V Primer

- Mi-V Ecosystem

- RISC-V Soft Processor Offerings

- Tools

- Debug

- Benchmarks

- Kits

- Mi-V Ecosystem for Linux

- Unleashed Expansion

- Demo Machine Learning

- Summary

#### What is RISC-V?

- A new, free, and open ISA developed at UC Berkeley

- Using a permissible BSD license

- ISA is designed for

- Simplicity: <50 instructions required to run Linux</li>

- Longevity: standardized instructions are fixed—your code runs forever

- RISC-V foundation set up to

- Protect the ISA

- Foster adoption

- RISC-V is not an open-source processor

- Although open-source implementations will exist

- Provides everyone an "architectural" license to innovate

# **RISC-V Working Groups/Chairs**

- Base ISA Ratification—Berkeley

- Bit Manipulation—AMD

- Compliance—Microsemi/Codasip

- Debug—SiFive

- Formal Spec—Bluespec

- Memory Model—NVIDIA, MIT

- Opcode Space Management—Berkeley

- Privilege Spec—SiFive

- SW Tool Chain—BAE

- Vector Extensions—Berkeley, Esperanto Technologies

- Security—Nvidia

| Esperanto —  |  |

|--------------|--|

| Technologies |  |

Bold = Microsemi Participation

## Why RISC-V for Soft CPUs?

- Open-source ISA

- Freedom to innovate at the micro-architectural level

- Allows for RTL inspection—trust and certifications

- Backed by industry leaders

- Longevity

- Fixed ISA for long-term code portability

- Easy migration to an ASIC

- Without negotiating a license from ARM

- Proprietary/closed alternatives

- ARM® Cortex-M1—encrypted RTL

- NIOS (Intel) and MicroBlaze (Xilinx), licensed

Open. Lowest Power. Programmable RISC-V Solutions.

## **Current SoC FPGA Offering**

| Features                | SmartFusion<br>ProASIC3, IGLOO         | SmartFusion2<br>IGLOO2                                     | PolarFire                                               |

|-------------------------|----------------------------------------|------------------------------------------------------------|---------------------------------------------------------|

| Logic Elements          | 100–30K                                | 5K-150K                                                    | 100K-480K                                               |

| Transceiver Rate        |                                        | 1 Gbps–5 Gbps                                              | 250 Mbps-12.7 Gbps                                      |

| I/O Speeds              | 400 Mbps LVDS                          | 667 Mbps DDR3<br>750 Mbps LVDS                             | 1600 Mbps DDR4<br>1.6 Gbps LVDS                         |

| DSP (18x18 Multipliers) |                                        | 240                                                        | 1480                                                    |

| Max RAM                 | 144 KB                                 | 5 MB                                                       | 33 MB                                                   |

| Processor Option        | 100 MHz ARM Cortex-M3                  | Soft RISC-V<br>166 MHz ARM Cortex-M3                       | Soft RISC-V<br>Crypto Co-Processor                      |

| On-Board Flash          | Up to 512 KB code store                | Up to 512 KB code store                                    | 56 KB secure NVM                                        |

| Family Type             | CPLD replacements<br>Smallest packages | Low-density FPGAs with more resources and the lowest power | Mid-range density FPGAs<br>Lowest power, cost optimized |

#### Hard Processor Subsystems, Soft RISC-V CPUs

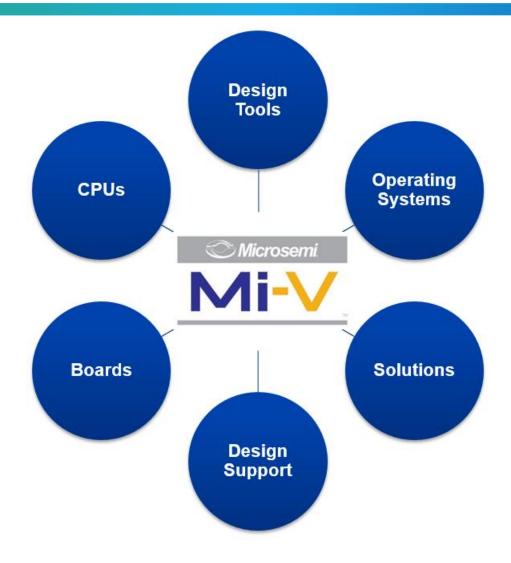

# Mi-V Ecosystem for PolarFire, RTG4, and IGLOO2 FPGAs

Open. Lowest Power. Programmable RISC-V Solutions.

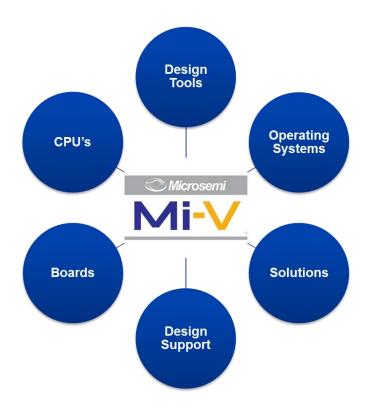

## **Mi-V Ecosystem Components**

A Comprehensive Ecosystem to Support RISC-V Development

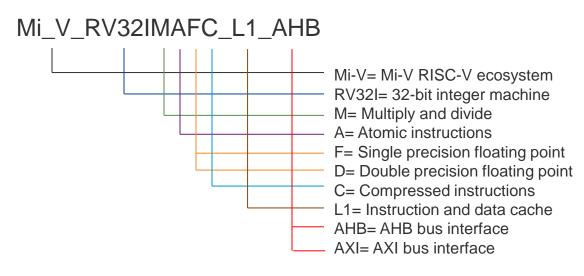

## **CPUs: Mi-V Soft CPU Roadmap**

| Core                  | LEs | CoreMark | Cache      | Mul/Div | Floating Point   | Availability |

|-----------------------|-----|----------|------------|---------|------------------|--------------|

| CORE_RISCV_AXI4       | 10K | 2.01     | 8K I and D | Yes     |                  | Now          |

| Mi_V_RV32IMAC_L1_AHB  | 10K | 2.01     | 8K I and D | Yes     |                  | Now          |

| Mi_V_RV32IMACF_L1_AHB | 26K | 2.01     | 8K I and D | Yes     | Single Precision | Now          |

| Mi_V_RV32IC_AHB       | 4K  |          |            |         |                  | Q2'18        |

- New Single Precision Floating Point core being released now

- Mi\_V\_RV32IC\_AHB

- Small core, without debug, estimate 4K LEs

- Additional cores to be added based on customer demand

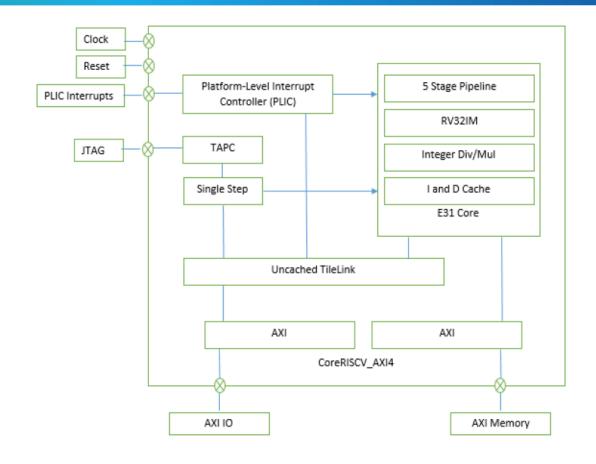

### Mi-V RISC-V Soft CPU on PolarFire/RTG4/IGLOO2 FPGAs

- 5-stage pipeline

- 8K I/D cache

- Integer mul/div

- 2 breakpoints

- 31 interrupts

- Priority by Int #

- 1.1 DMIPS/MHz

- 10K LEs

- 50 MHz–150 MHz

- Depending on product

### **Boot Sources for Mi-V RISC-V Soft CPUs**

|                | Non-Volatile Source |          |         |           |  |

|----------------|---------------------|----------|---------|-----------|--|

| Product Family | On-C                | Off-Chip |         |           |  |

| ,              | sNVM                | uPROM    | eNVM    | SPI Flash |  |

| PolarFire      | 56                  | 37–64    |         | <b>✓</b>  |  |

| RTG4           |                     | 46       |         | ✓         |  |

| IGLOO2         |                     |          | 128–512 | ✓         |  |

sNVM PUF-protected R/W NVM

uPROM Read-only NVM

eNVM R/W NVM

The Only FPGA Supplier with Secure Boot Built-In and Open, Inspectable CPUs

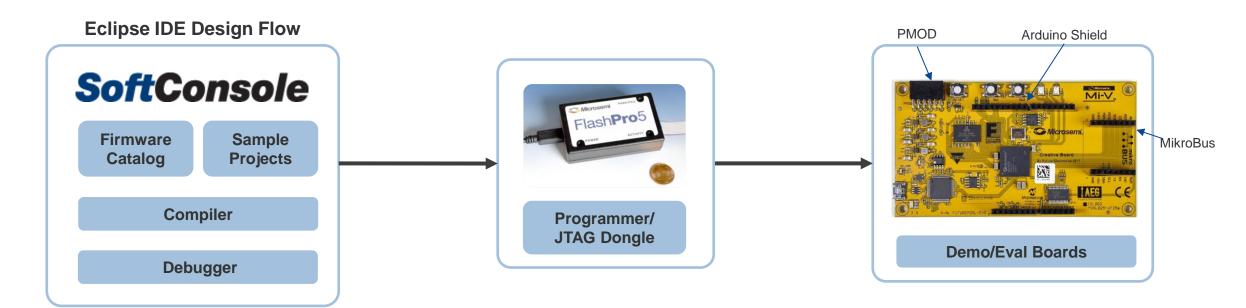

## SoftConsole Eclipse IDE

- A single tool chain for RISC-V and ARM MCUs

- Easy migration from ARM to RISC-V

- Running on Linux or Windows hosts

- Supported by a Tier 1 supplier

- Bundled with example projects and RTOSs

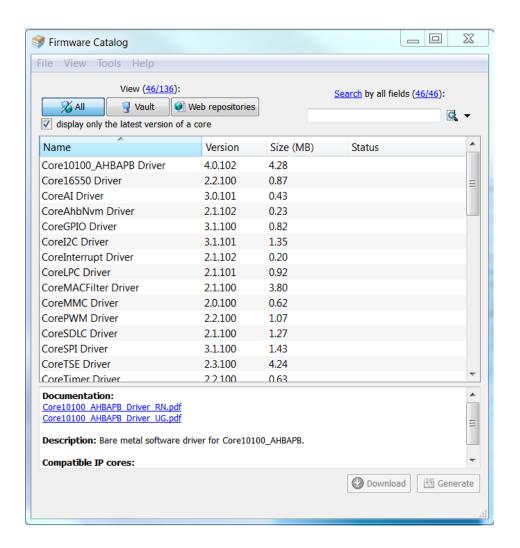

## **Firmware Catalog**

- Drivers for Microsemi RISC-V soft CPUs

- Updates pushed to your desktop

- Release notes

- User guides

- Version controlled

- MISRA/Netrino compliant

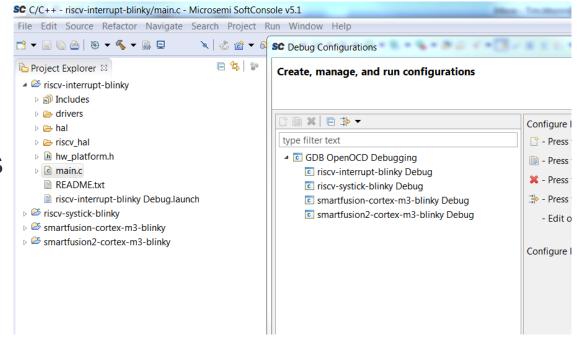

## **Software Debug**

- Soft CPUs support 8 breakpoints

- GDB open OCD debug

- OpenOCD supports a wide range of dongles

- FlashPro5

- Olimex ARM-USB-TINY-H

### **Boards: Mi-V Platforms**

- Microsemi Soft CPUs on FPGAs

- PolarFire

- RTG4

- IGLOO2

- SiFive Freedom Unleashed Platforms

- HiFive1 FE310 Arduino platform validated with SoftConsole

Mi-V IGLOO2 Creative Development Board

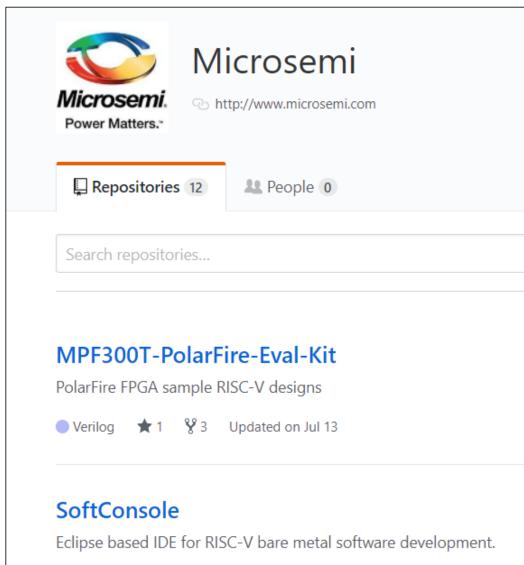

## Solutions: Example Designs on Github

- Design examples targeted to various boards

- Hello world printf through UART

- Interrupt blinky

- Touch screen tic-tac-toe

- Crypto processor with RISC-V

- Getting started building a RISC-V tutorial

- RISC-V hardware abstraction layer to port from Cortex-M

## Operating Systems: Mi-V RISC-V Soft CPU RTOS Support

- Open Source

- FreeRTOS

- Huawei LiteOS

- MyNewt

- Zephr (Hifive)

- Commercial

- ExpressLogic—ThreadX

- SiLabs—Micrium µC/OSIII

# MicroPython

# **Mi-V Supporting Linux**

## Mi-V HiFive Unleashed Expansion: Advancing the Ecosystem

- Enables the community to port tools, OS's, middleware, packages to RISC-V

- Makes software development easier

- Enables standard and custom peripherals

- Supporting the community supports our soft CPUs for our FPGAs

- Supporting the community supports the MI-V ecosystem and vice versa

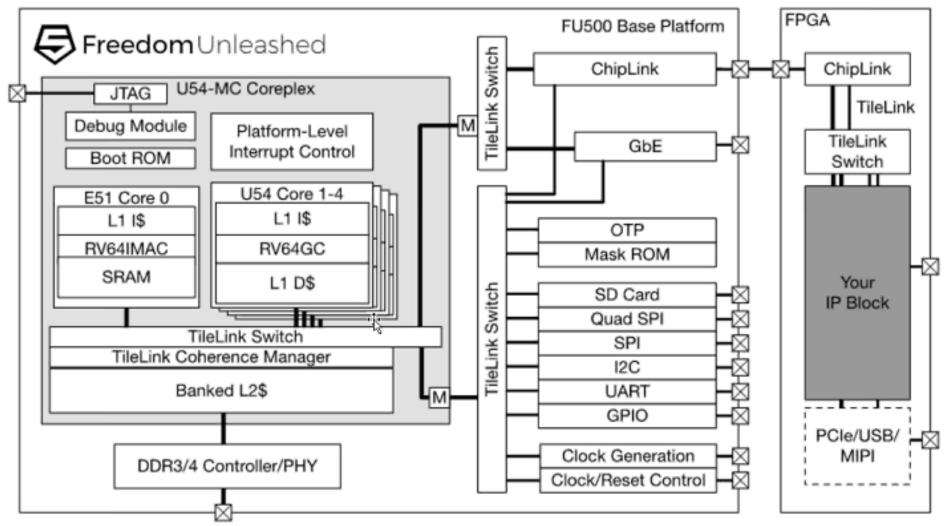

## SiFive U-54 Block Diagram and Partnership

TSMC Shuttle Run October

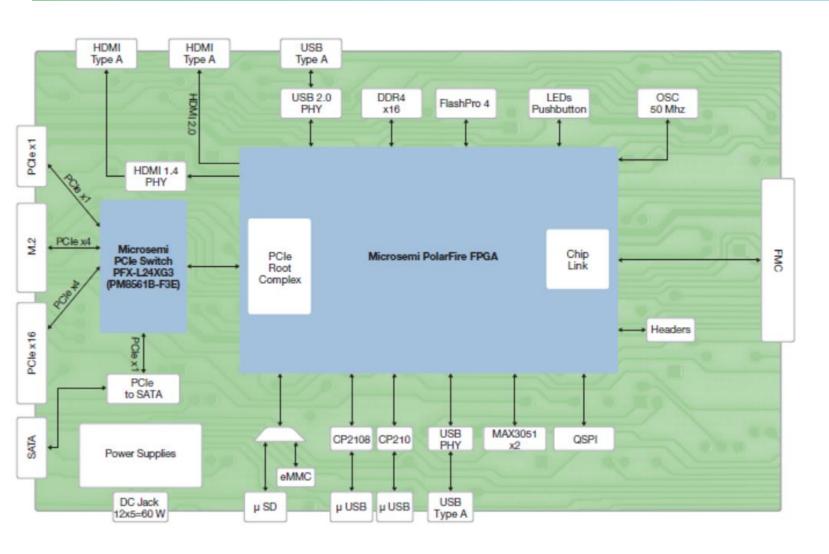

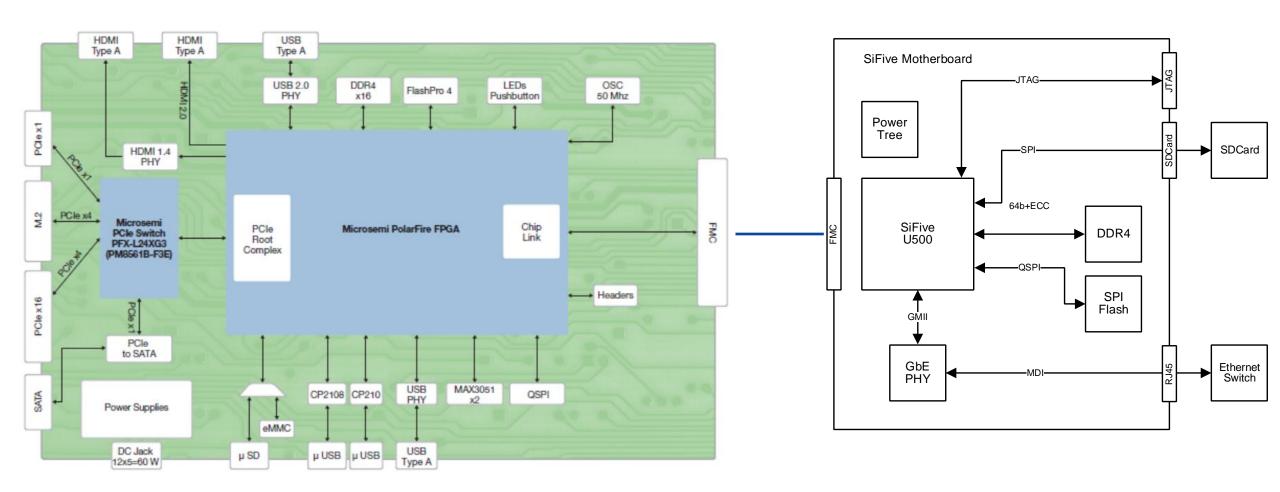

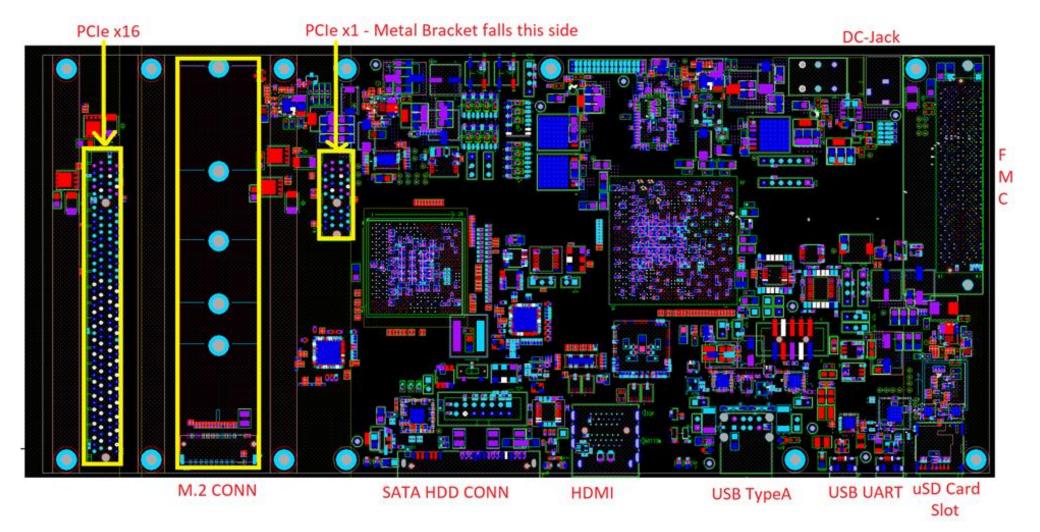

## PolarFire HiFive Unleashed Development Platform

- Designed for Expandability

- Pre-programmed with a ChipLink to PCIe Root Port Bridge

- Enables Root Complex on the HiFive Unleashed **Board**

- Stay tuned for FPGA developer versions

# Microsemi Mi-V HiFive Unleashed Expansion Board

## PolarFire Mi-V HiFive Unleashed Development Platform

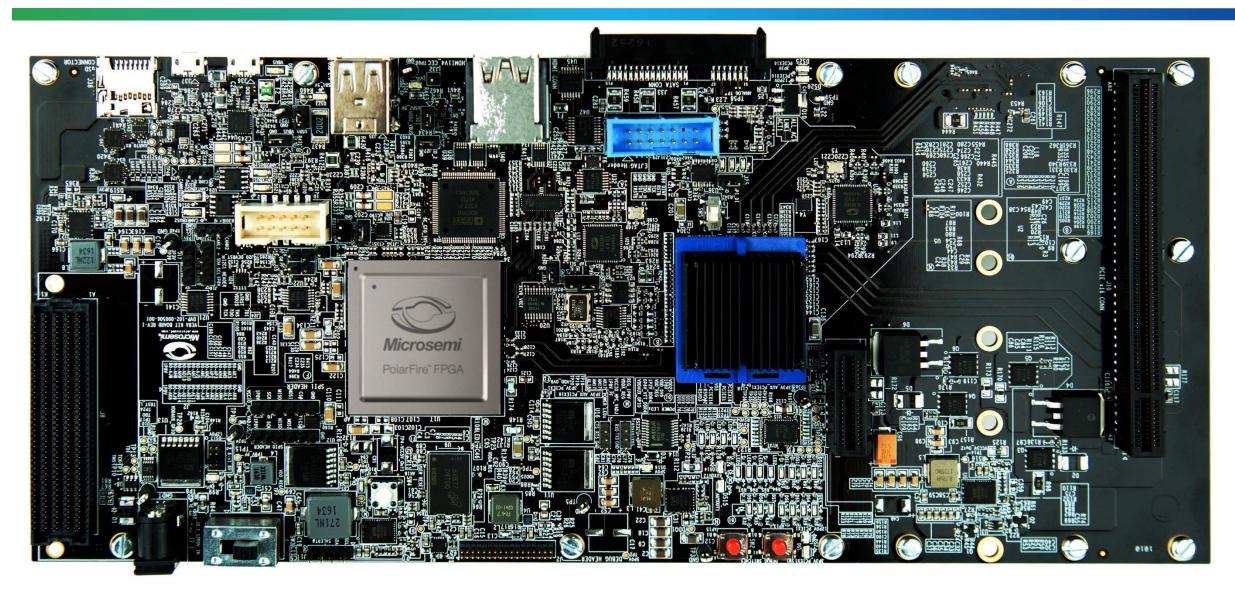

## **HiFive Unleashed + Unleashed Expansion Board**

## All the Peripherals You Need to Build a RISC-V PC

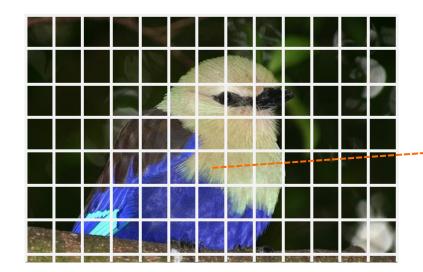

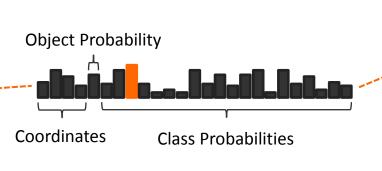

## **ASIC Design Services – Deep Learning IP**

#### Tiny-YOLOv2

- Fully Convolutional Neural Network 9 Convolutional Layers

- convolution operation + batch normalisation + activation + pooling

- Trained end-to-end on Pascal VOC dataset

- Quantized and finetuned from provided base network by Joseph Redmon

- Tiny YOLO @ https://pjreddie.com/darknet/yolo/

Core Deep Learning an embedded FPGA solution

Multiple predictions per grid location

## **PolarFire Tiny Yolo Video**

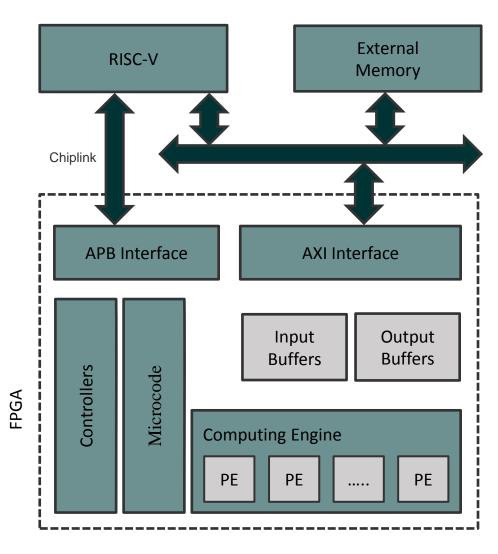

## **Core Deep Learning Block Diagram**

#### Core Architecture

#### **Core generator features**

- Full pipeline from convolutional neural network description to FPGA implementation

- Network retraining for memory footprint minimisation

- Support for different network layers

- Convolutional layer

- Fully connected layer

- Pooling layer

- Activation layers

## Mi-V RISC-V Soft CPU Summary

- A roadmap of soft CPUs for Microsemi FPGAs, royalty free

- Standardized ISA to protect your software investment

- Portable RTL for high-volume customers to migrate to an ASIC

- Security customers can inspect the RTL for trust

- Enables avionics and safety certification with viewable RTL

- Supported by industry-standard open-source tools

Open. Lowest Power. Programmable RISC-V Solutions.

## Mi-V HiFive Unleashed Expansion Summary

- Accelerates the RISC-V Linux Ecosystem

- Enable the community to port tools, OS's, middleware, packages to RISC-V

- Supporting the community supports our soft CPUs for our FPGAs

- Supporting the community supports the MI-V ecosystem and vice versa

- Deep Learning Core demo uses

- Debian Linux, Xserver, OpenCV, V4L, PCIe and more were used

### Thank You

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136

Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

email: sales.support@microsemi.com

www.microsemi.com

©2018 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 4,800 employees globally. Learn more at www.microsemi.com

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.