# Pushing Data from Edge to Cloud with RISC-V Ecosystem

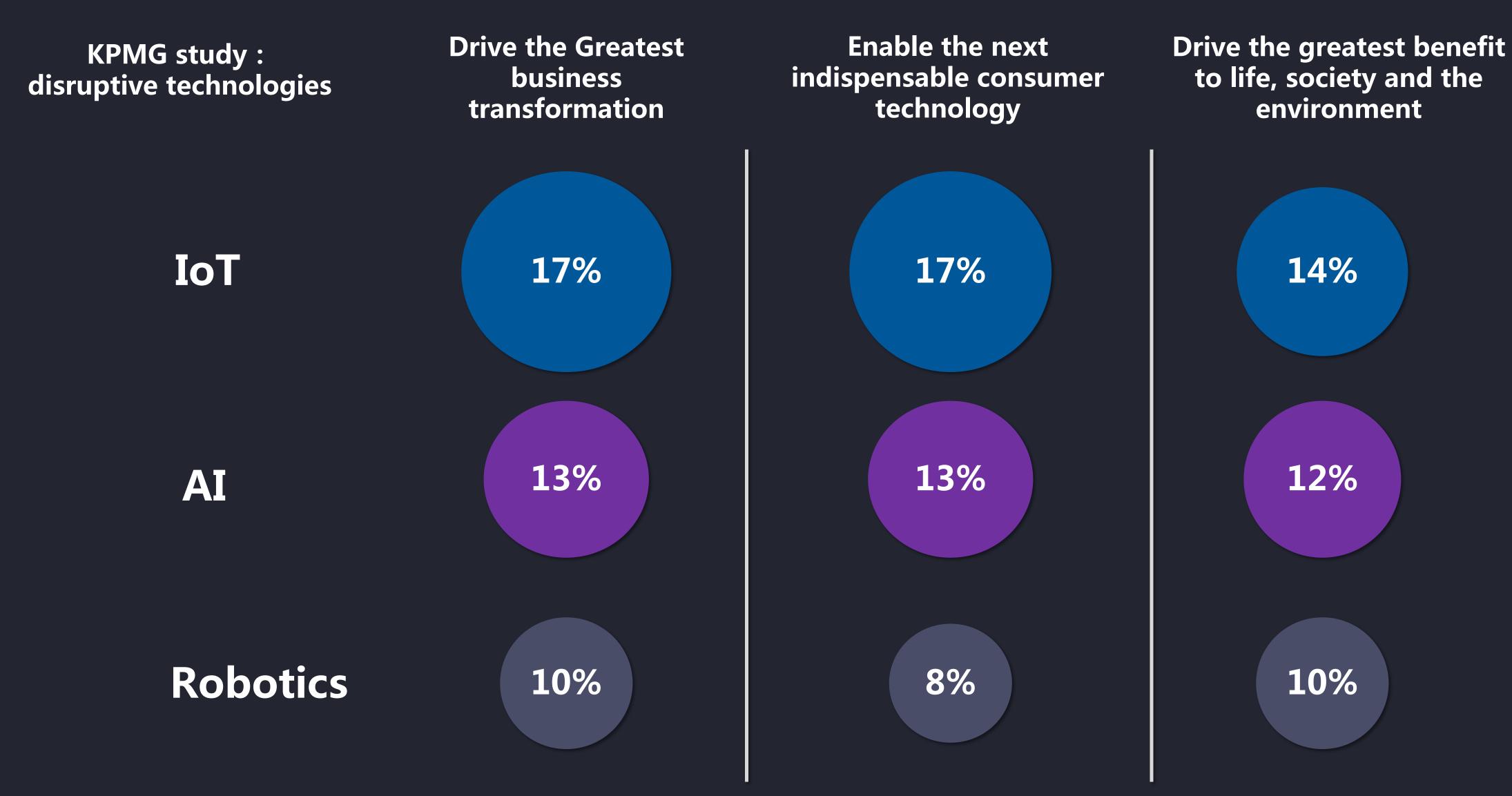

## IoT Becomes the Main Driver for Top Techs

Source: KPMG, 2018

- High cost of NRE

- Intricate design flows

- Fragmented IoT market

Efficiency translates into market share, profit margin and experience

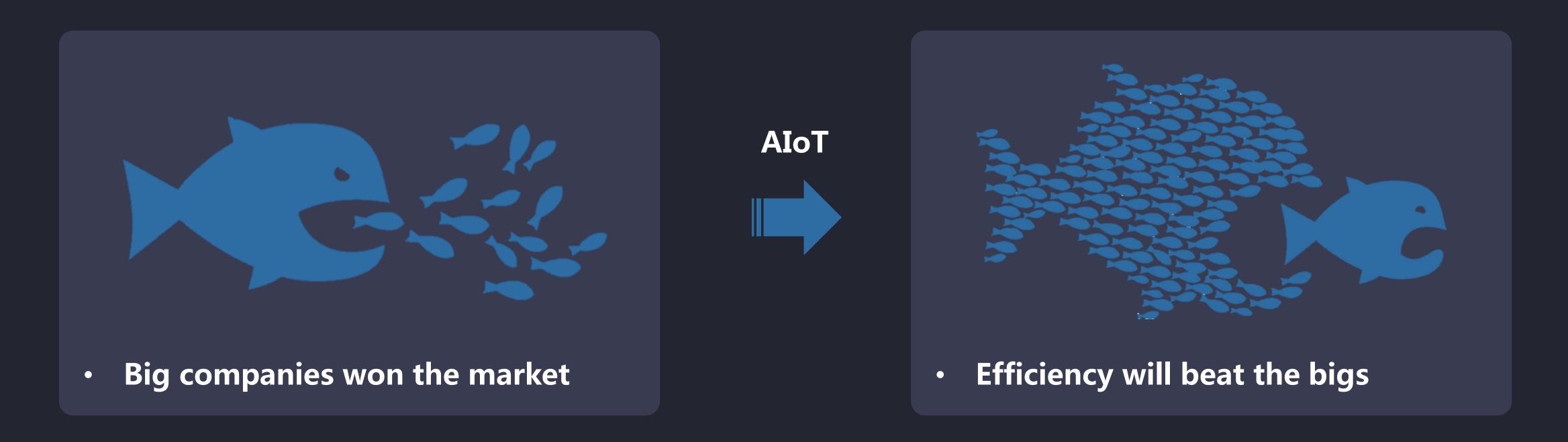

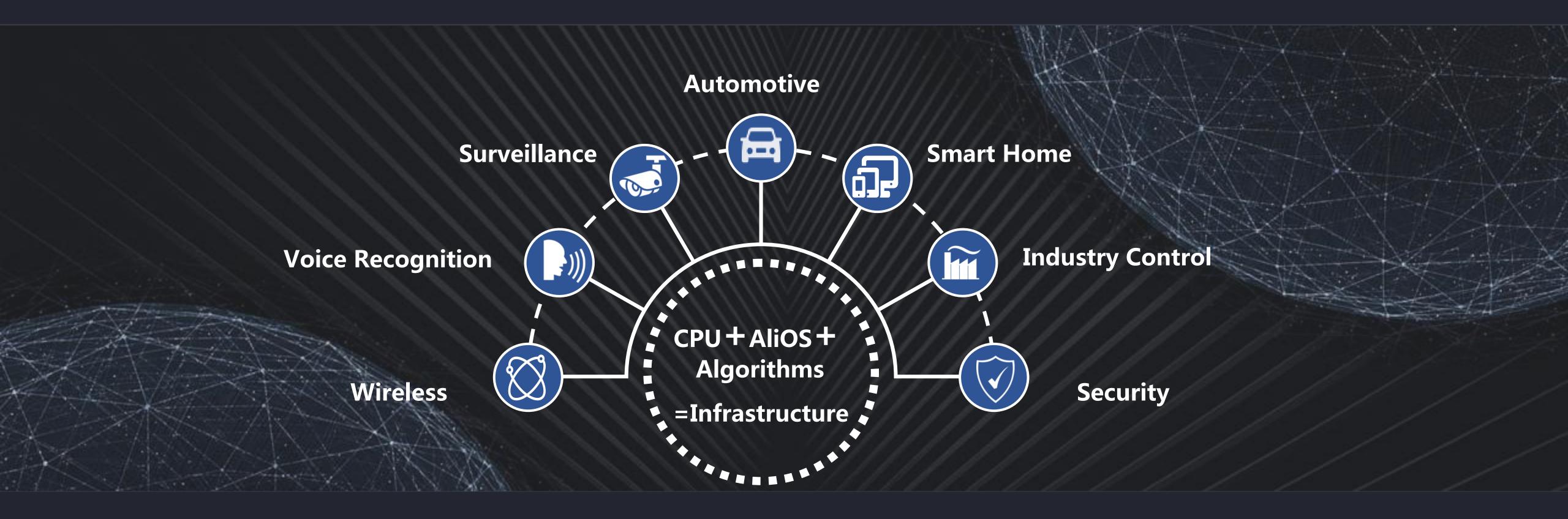

## Alibaba as Infrastructure Provider Boosts Industrial Efficiency

**Infrastructure Provider in the AIoT Era**

Security

Intelligent Computing

• • •

**Industry Control**

Memory Control

Alios

Domain Specific SoC Platforms (IPs from Partners)

**Self Defined CPU+RISC-V Compatible**

**Domain Specific Architecture**

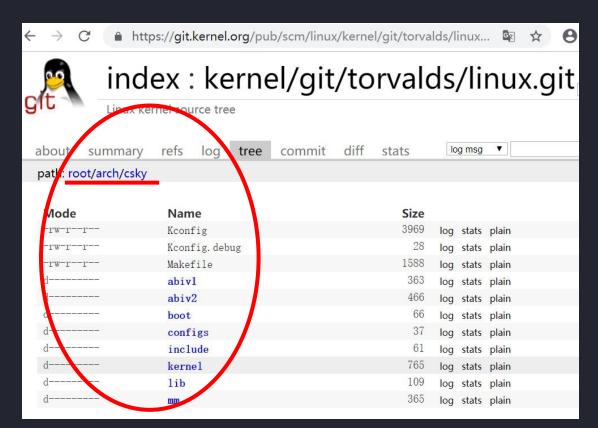

## Accumulated Comprehensive Experience in CPU IPs

GCC, the GNU Compiler C The GNU Compiler Collection includes front ends for C, C++, Objective-C as well as libraries for these languages (libstdc++,...). GCC was originall compiler for the GNU operating system. The GNU system was develope We strive to provide regular, high quality releases, which we want to wor native and cross targets (including GNU/Linux), and encourage everyone changes or help testing GCC. Our sources are readily and freely available Major decisions about GCC are made by the steering committee, guided Supported R News GCC 8.2 (chan Status: 201 GCC support for C-SKY V2 processors has been added. This back end was contributed by C-SKY GCC 7.3 (chan Status: 201 Held in Manchester, September 7-9 2018

IC Cards

AI

### **GNU & Linux Supported**

#### Surveillance

#### Printer

**Smart Grid**

MCU

**Info Security**

**NET&COMM**

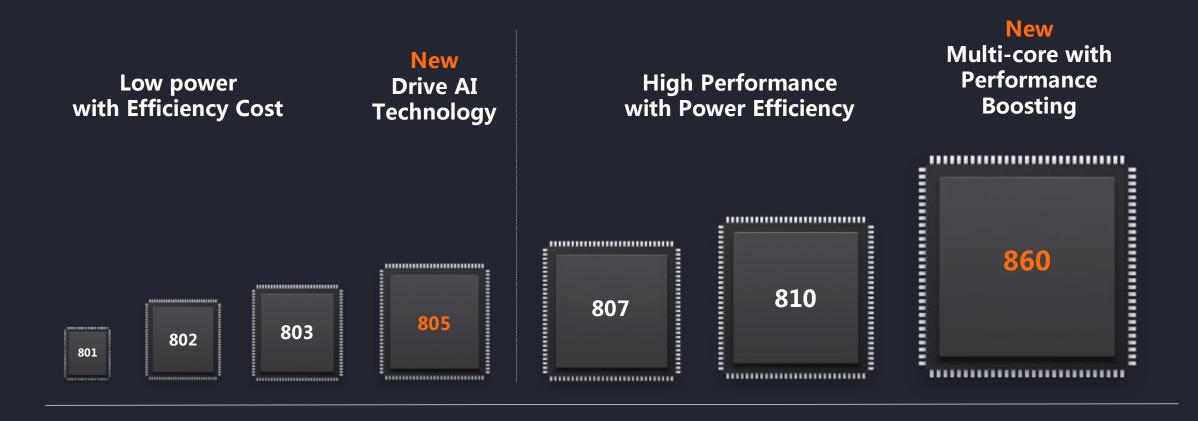

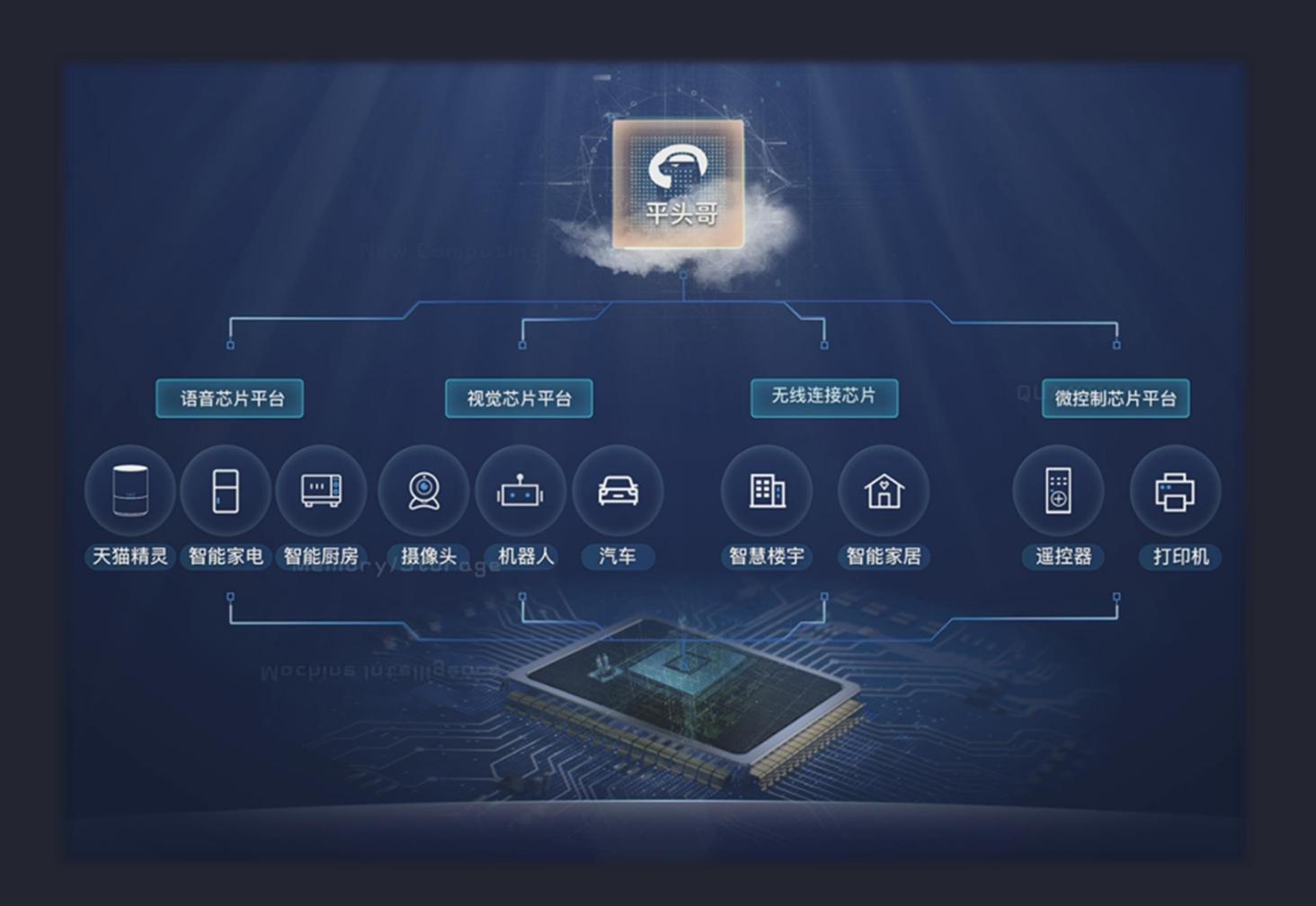

## AIoT Domain Specific SoC Platform

Software & Hardware Integrated IoT IC Design Infrastructure

World's first embedded RISC-V core with TEE

World's first-class high performance RISC-V CPU

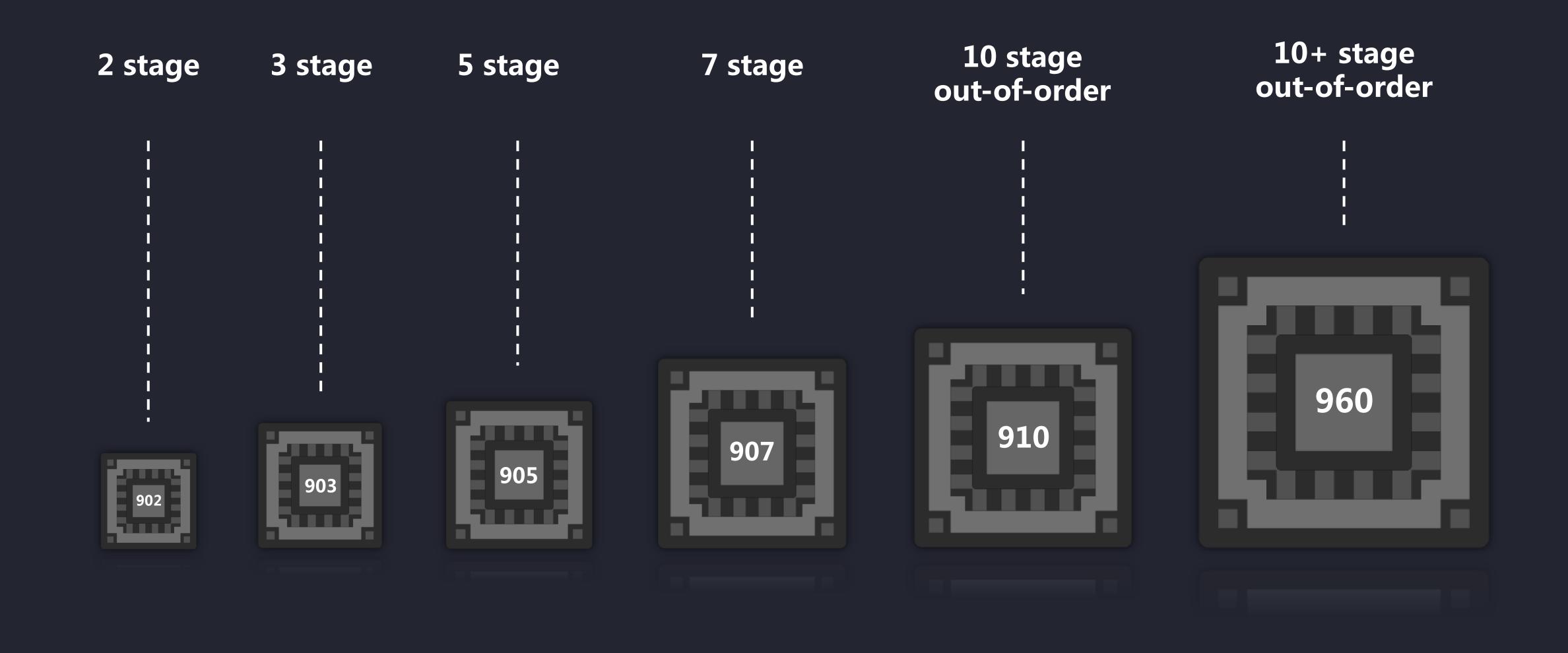

## RISC-V Product Lines

Ε

**EMBEDDED**

IoT , MCU R

REALTIME RELIABLE

SSD , Industrial control Ι

INTELLIGENCE

AI , DSP S

**SECURITY**

Info Security,

Mobile Payment

**COMPUTING**

5G, Smart Surveillance

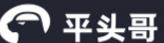

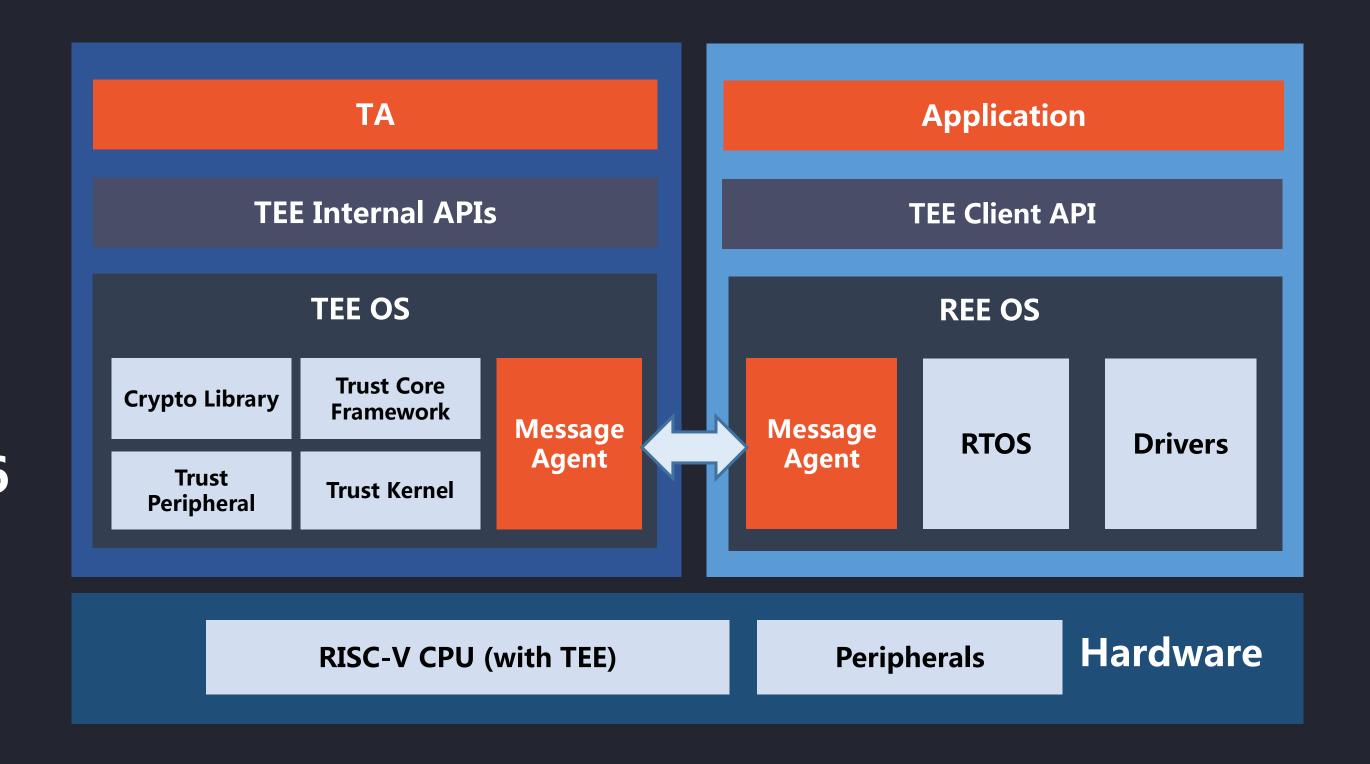

### 902 - World's First Embedded RISC-V Core with TEE

- Two virtual cores: trusted and untrusted

- Trust state for sensitive code

- Hardware isolation for trusted and untrusted resources

- Non-aligned memory protection: up to 16 continuous spaces

- Trusted interrupt extension

- Trusted debug extension

## Supported by AliOS

# Tech Specs

- RISC-V RV32EMC;

- 2 stage in-order pipeline;

- Machine and user mode support;

- Configurable hardware multiplier;

- Configurable tightly coupled IP;

- Configurable cache;

- 10K EQG for minimum configuration

### Low Cost, Low Power

3.8 uW/MHz per @ TSMC40LP, 9-track, typical corner

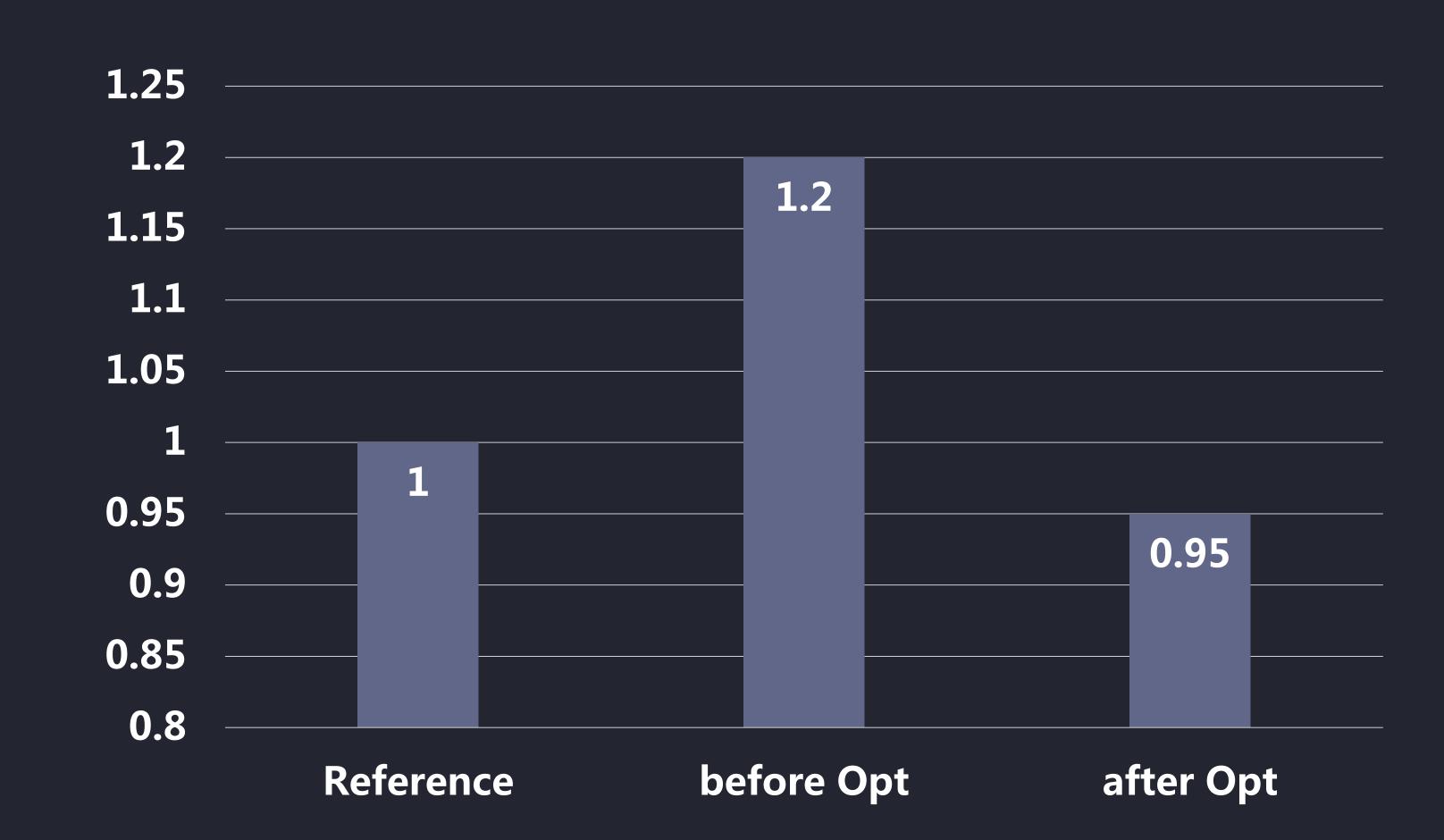

## **Automatic Assessment Tool for ISA Optimization**

## ISA (Description Language)

# Code Density

```

{"name": "addi.sps", "imm": "[4~256]>>2", "rd": "10~15", "rs1": null, "rs2": null, "rs3": null}, {"name": "addi", "imm": "1,-1", "rd": "1,5~15", "rs1": "1,5~15", "rs2": null, "rs3": null}, {"name": "addi", "imm": "2,4,8,12", "rd": "8~15", "rs1": "8~15", "rs2": null, "rs3": null}, {"name": "addi", "imm": "2,4,8,12", "rd": "8~15", "rs1": "8~15", "rs1": "rd", "rs2": null, "rs3": null}, {"name": "addi", "imm": "2,4,8", "rd": "5~7", "rs1": "rd", "rs2": null, "rs3": null}, "rs3": null}, {"name": "addi", "imm": "[6-6~-2,2,3,5~7,9~16", "rs1": "rd", "rs2": null, "rs3": null}, "rs3": null, "rs

```

# **Evaluation System**

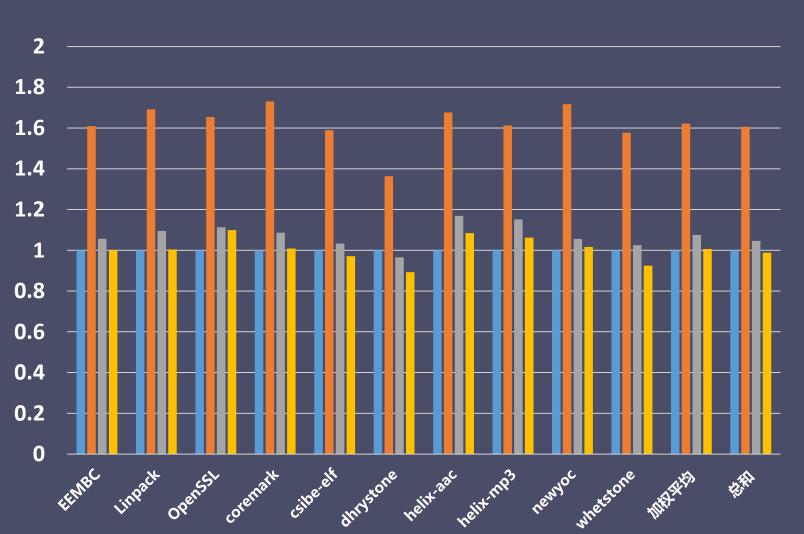

## **Highly Improved Code Density**

#### **Benchmark List**

- EEMBC

- Linpack

- OpenSSL

- Coremark

- Dhrystone

- Helix

- Newyoc

- Whetstone

## Active Contributor to RISC-V Ecosystem

# **Security Solution**

- Trust execution environment

- Mitigation attack solution

- Trust IoT stack

- Secure YoC platform

#### Linux

- Perf supported

- Memory usage efficiency (IOMMU)

- Memory model optimization

# Software Tools

- First IDE supporting profiling

- Trace supported on simulator

- High performance instruction subsets

#### **EABI**

- Definition of param-register

- Redefinition of register usage

- Quantitative data on the impact of code density

• • •

## **Edge-to-Cloud Ecosystem**

- Edge-to-Cloud Infrastructure

- Algorithmic Ability

#### Customer

- Scenario Definition

- Application Algorithms

Enable customers to deliver competitive products with high efficiency