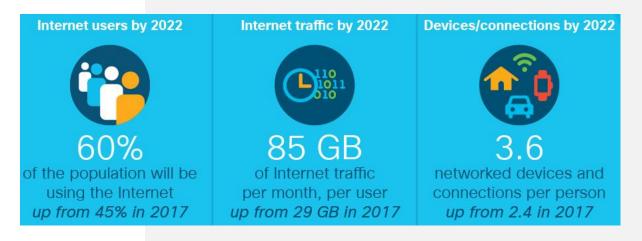

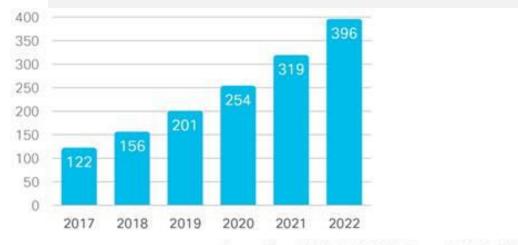

# **Global Trends**

Exabytes per Month

Source: Cisco VNI Global IP Traffic Forecast, 2017-2022

# SiFive Core IP Embedding Intelligence Everywhere

#### **Consumer**

AR/VR/Gaming devices

Smart Home

Imaging/Wearables

## **Storage/Networking/5G**

SSD, SAN, NAS

Base Stations, Small cells, APs

Switches, Smart NICs, Offload cards

## ML/Edge

Sensor Hubs, Gateways

Autonomous machines

IoT devices

# SiFive 7 Series Core IP

The **highest performance** commercial **RISC-V** processor IP

32-bit Embedded Processors

64-bit Embedded

Processors

64-bit Application Processors

Common Feature sets

Hard Real-time capabilities

Unprecedented scalability

~60% increase in CoreMarks/MHz\*

~40% increase in DMIPS/MHz\*

10% increase in Fmax\*

# **Core IP 7 Series Standard Cores**

01 E76, E76-MC

S76, S76-MC

U74, U74-MC

### **SiFive Core IP Portfolio**

**E** Cores

**32-bit embedded cores** MCU, edge computing, AI, IoT

**S** Cores

**64-bit embedded cores** Storage, AR/VR, machine learning

**U** Cores

**64-bit application cores** Linux, datacenter, network baseband

#### 7 Series

Highest performance: 8-stage, dual-issue

superscalar pipeline

**E7 Series**

> E76-MC Compare to Cortex-M7

Quad-core 32-bit embedded processor

E76 Compare to Cortex-M7

High performance 32-bit embedded core

High-

#### **S7 Series**

> S76-MC No 64-bit Cortex equivalent Quad-core 64-bit embedded processor Multicore:

> \$76 No 64-bit Cortex equivalent > U74

High-performance 64-bit embedded core High

#### **U7 Series**

U74-MC Compare to Cortex-A55 MP4 Multicore: four U74 cores and one S76 core

> U74 Compare to Cortex-A55 High performance Llnux-capable processor

#### 3/5 Series

Efficient performance:

5–6-stage, singleissue pipeline

#### E3 Series

**E34** Compare to Cortex-R5F E31 features + single-precision floating point

**E31** Compare to Cortex-R5 Balanced performance and efficiency

#### S5 Series

> **S54** No 64-bit Cortex equivalent S51 features + single-precision floating point Multicore a

> **S51** No 64-bit Cortex equivalent Low-power 64-bit MCU core

#### **U5 Series**

Multicore application processor with four U54 cores and one S76 core

> **U54** Compare to Cortex-A53 Linux-capable application processor

### 2 Series

Power & area optimized:

2-3-stage, singleissue pipeline

#### **E2 Series**

> **E24** Compare to Cortex-M4F E21 + single-precision floating point

**E21** Compare to Cortex-M4 E20 + User Mode, Atomics, Multiply, TIM

**E20** Compare to Cortex-M0+ Our smallest, most efficient core

#### S2 Series

S21 No 64-bit Cortex Equivalent

Area optimized 64-bit processor

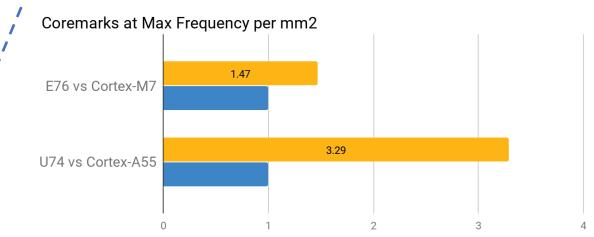

## 7-Series Core IP – Efficient Performance vs. Legacy ISA

|                 | SiFive<br>E76        | Arm<br>Cortex-M7     | SiFive<br>U74       | Arm<br>Cortex-A55     |

|-----------------|----------------------|----------------------|---------------------|-----------------------|

| Instruction Set | 32-bit RISC-V        | 32-bit Arm v7-M      | 64-bit RISC-V       | 64-bit Arm v8         |

| Max Clock Freq  | 1.6GHz†              | 1.1GHz               | 1.6GHz†             | 1.6GHzt               |

| Max IPC         | 2 IPC                | 2 IPC                | 2 IPC               | 2 IPC                 |

| CoreMark Perf   | 4.9CM/MHz            | 5.0CM/MHz            | 4.9CM/MHz           | 4.4CM/MHz†            |

| Die Area*       | 0.065mm <sup>2</sup> | 0.067mm <sup>2</sup> | 0.22mm <sup>2</sup> | 0.65mm <sup>2</sup> † |

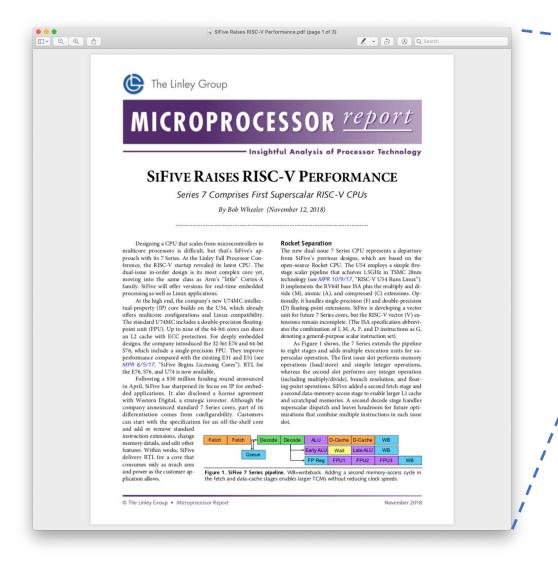

**Table 1. SiFive-versus-Arm CPU comparison.** The new dual-issue 7 Series delivers integer performance on a par with that of Arm's comparable CPUs. All metrics assume TSMC 28nm HP technology. \*Without memories. (Source: vendors, except †The Linley Group estimate)

source: https://www.linleygroup.com/mpr/

## **Efficiency**

- Configure and use the right core for the job

- Power down large cores and memories when not needed

## **Performance**

- Instant response times with realtime capable cores

- High-performance compute available when needed

# — SiFive 7 Series

# **Embedded Intelligence Everywhere**

**Scalable throughput** provided by **8+1** cores per cluster

**Extensible design** via custom instructions

Configurable memory architecture for application specific tuning

U7Series Core Core PLIC РМР Debug I\$ w/ECC DTIM w/ECC D\$ w/ECC **Bus Matrix** Peripheral Port L2 Cache with ECC System Port Front Port **Memory Port** TileLink or AMBA

**Enhanced determinism** for hard real-time constraints

Functional safety provided by in-built fault tolerance mechanisms

A **single** pre-integrated and verified deliverable

**Tightly integrated memor**y for low

latency access

**64-bit addressability** for real time latency sensitive applications

**Mixed-precision arithmetic** for efficient compute of ML workloads

**Cache lock capability** for mission-critical computing

In-cluster coherent combination of real-time and application processors

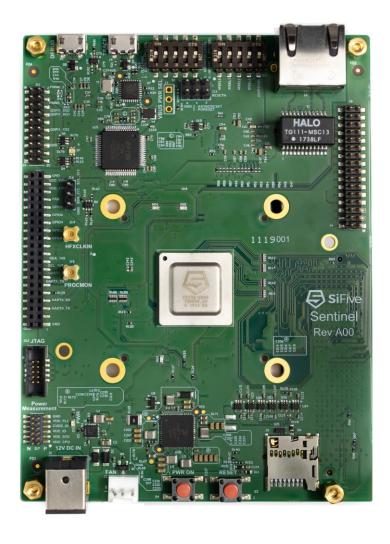

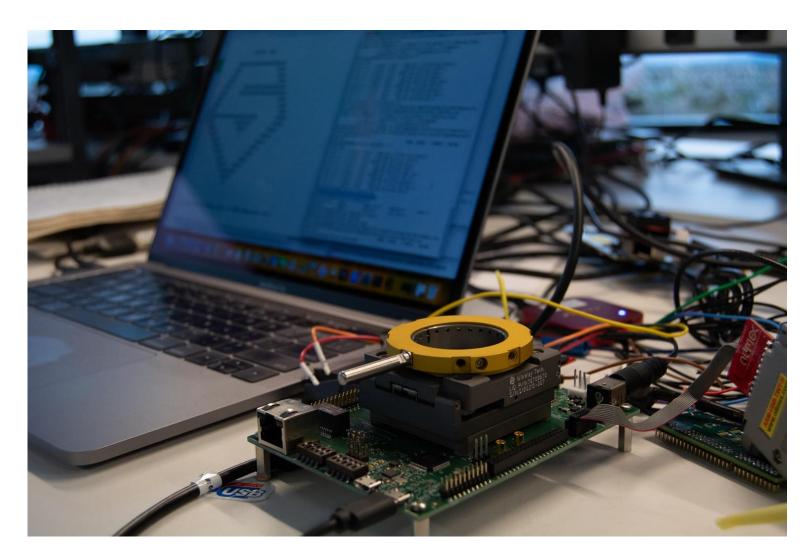

## **7-Series Core IP Proven in Silicon**

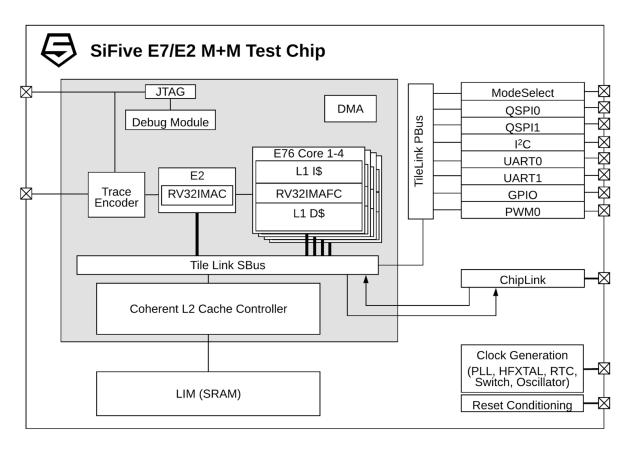

## **Showcasing SiFive Mix+Match Architecture**

# Heterogeneous Multicore

- 4x SiFive E76 Cores

- 1x SiFive E21 Core

# Coherent L2 Memory Subsystem

- L2 Cache with way-locking and directly addressable memory

- Large cacheable SRAM on chip

## Instruction Trace

SiFive RISC-V silicon with instruction trace capabilities

# ChipLink

Coherent off-chip access

# **Enterprise SSD**

- FADU Annapurna SSD Controller

- World's first RISC-V SSD controller

- FADU Bravo Series Enterprise SSD

- 3.5GB throughput and 800K IOPS at less than 1.8W

- Powered by SiFive E51

"SiFive's RISC-V Core IP was **1/3 the power** and **1/3 the area** of competing solutions, and gave FADU the flexibility we needed in optimizing our architecture to achieve these groundbreaking products." J. Lee, FADU CEO

# **Intelligent Edge**

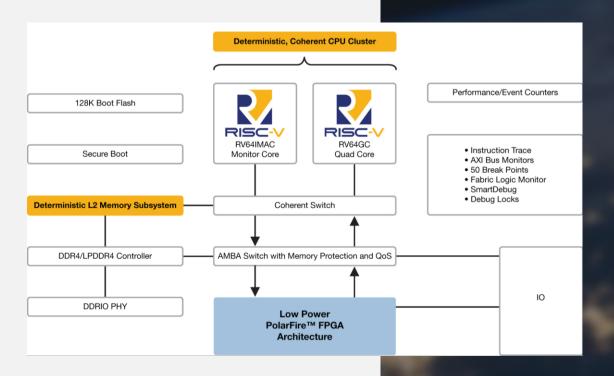

- Microsemi's PolarFire SoC

- World's first RISC-V SoC FPGA architecture bringing Real-time to Linux

- Targeted for real-time Linux applications at the Edge

- **Defense-grade** security features

- Secure boot

- DPA safe crypto core

- SECDED on all memories

- Physical memory protection/PMP

- Powered by SiFive U54-MC and SiFive E51

# **Wearable Al**

- Huangshan No. 1 (MHS001) from Huami using Upbeat Tech

- Integrated biometric signal processor with 4 dedicated AI engines and built-in CNN based inference engine

- 38 percent more efficient than the Arm Cortex-M4

- Powered by SiFive E31

"The world's first artificial intelligence powered wearable chipset"