# SHAKTI Processor Project

**Arjun Menon**

Senior Project Officer RISE Group | IIT Madras

# **Processor IPs**

# **Processor IPs**

### Features:

- 3-stage in-order

- ISA: RV[32/64] I [ACM]

- Can boot FreeRTOS, Zephyr

## **E-Class**

Src: <a href="https://gitlab.com/shaktiproject/cores/e-class">https://gitlab.com/shaktiproject/cores/e-class</a>

### Artix-7 FPGA

| Config      | RV32IACM | RV64IACM |

|-------------|----------|----------|

| LUTs        | 2.5K     | ЗК       |

| Clock freq. | 100 MHz  | 100 MHz  |

### 180nm ASIC

| Config      | RV32IACM | RV64IACM |

|-------------|----------|----------|

| Instances   | 22.6K    | 40.7K    |

| Clock freq. | 100 MHz  | 100 MHz  |

# **Processor IPs**

### Features:

- 5-stage in-order

- ISA: RV[32/64] I [ACFDMNSU]

- Branch predictor + RAS

- Daisy-chained CSRs

- 1.72 DMIPS/MHz

- Can boot Linux kernel

Prototypes

180nm 22nm (LP)

Src: <a href="https://gitlab.com/shaktiproject/cores/c-class">https://gitlab.com/shaktiproject/cores/c-class</a>

### Artix-7 FPGA

|             | RV32IACMNSU | RV64IACMNSU |

|-------------|-------------|-------------|

| LUTs        | 4.5K        | 6.5K        |

| Clock freq. | 100 MHz     | 80 MHz      |

### 65nm ASIC (LP)

|             | RV32IACMNSU | RV64IACMNSU |

|-------------|-------------|-------------|

| Instances   | 40.2K       | 80K         |

| Clock freq. | 400 MHz     | 340 MHz     |

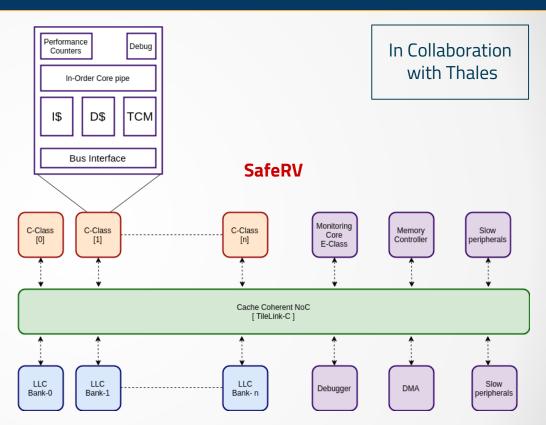

# **Core Configuration**

# Multicore

- Parameterizable no. of application cores (1-32 cores)

- Directory-based MSI cache coherence

- System management with monitor core

- TileLink-C bus protocol

- NoC with mesh topology

# Safety critical applications

- Criticality aware NoC

- Triple Lock-Step (TLS)

pipeline for fault tolerance\*

# **Uncore IPs**

- Bus protocols

- o AXI4/AXI4-Lite

- o TileLink-U/H

- Bridges to/from AXI4 and AXI4-Lite with different data bus widths and clocks

- Posit-arithmetic Units + Compiler

- Peripherals

```

o SPI

```

**PWM**

- Quad SPITimers

- o I2C

Watchdog

o DMA

0

# Offerings

#### Core + Uncore IP

- Various classes of processors

- Bus protocols

- Peripherals •

- Fully automated FPGA bitstream generation

#### Verification

- CoCoTb VIPs: Coroutine Co-simulation Verification IPs\*

- AAPG: Automatic Assembly Program Generator

- RiTA: RISC-V Trace Analyzer

- RISCV-Config Legalizer

- RISCOF: Compliance Testing

- RiVer: RISC-V Verification as a plugin infrastructure\*

### **Software**

- Integrated Development Environment (IDE)

- Software Development Kit (SDK)

- RISC-V OCaml and Mirage OS\* •

### Research\*

- Systolic Array

- Crypto accelerators

- Side-channel attack resistance

- Fat-pointers

- Compartmentalization

Start using Shakti today!

https://shakti.org.in