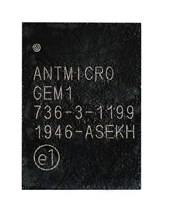

Antmicro’s GEM developed in collaboration with zGlue and other partners is a series of chiplet-based ASICs that is meant to encapsulate the design complexity of a custom chip in a small form factor within a practical, quick-prototyping / quick-tape-out process. Thanks to zGlue’s technology, customers will be able to use Antmicro’s services to miniaturize their multi-component design into a 6×9 mm chip much faster than using traditional methods, and will be free to combine RISC-V and ARM CPUs, FPGAs, sensors, radios and other functional elements for their specific applications.

“Antmicro and zGlue share a common vision and value proposition to accelerate time-to-market for hardware innovation,” said Ming Zhang, Co-founder and CEO, zGlue, “Our partnership is centered on enabling all stages of the value chain to quickly realize the business benefits that RISC-V technology has been promising.”

Antmicro’s GEM developed in collaboration with zGlue and other partners is a series of chiplet-based ASICs that is meant to encapsulate the design complexity of a custom chip in a small form factor within a practical, quick-prototyping / quick-tape-out process. Thanks to zGlue’s technology, customers will be able to use Antmicro’s services to miniaturize their multi-component design into a 6×9 mm chip much faster than using traditional methods, and will be free to combine RISC-V and ARM CPUs, FPGAs, sensors, radios and other functional elements for their specific applications.

“Antmicro and zGlue share a common vision and value proposition to accelerate time-to-market for hardware innovation,” said Ming Zhang, Co-founder and CEO, zGlue, “Our partnership is centered on enabling all stages of the value chain to quickly realize the business benefits that RISC-V technology has been promising.”

With experience in open architectures such as RISC-V and associated emerging technologies, Antmicro offers custom engineering services to build software-driven ASICs, matching PCBs as well as the complete software based on modern and open solutions such as the Zephyr RTOS or Linux, tooling and testing suites, as well as AI functionalities.

The chip presented for the first time today at the annual RISC-V Summit will be on display at Antmicro’s booth #202 and zGlue’s booth #100 in the exhibitor area throughout the event. The current demonstrator is a GEM1 chip featuring two Lattice iCE40 FPGAs with a MIPI CSI-2 switch. A hard RISC-V and Lattice iCE40 FPGA version, named the GEM2 and developed in collaboration with efabless, has also been manufactured and will be released soon.

For more information contact Antmicro at contact@antmicro.com or zGlue at info@zglue.com.

With experience in open architectures such as RISC-V and associated emerging technologies, Antmicro offers custom engineering services to build software-driven ASICs, matching PCBs as well as the complete software based on modern and open solutions such as the Zephyr RTOS or Linux, tooling and testing suites, as well as AI functionalities.

The chip presented for the first time today at the annual RISC-V Summit will be on display at Antmicro’s booth #202 and zGlue’s booth #100 in the exhibitor area throughout the event. The current demonstrator is a GEM1 chip featuring two Lattice iCE40 FPGAs with a MIPI CSI-2 switch. A hard RISC-V and Lattice iCE40 FPGA version, named the GEM2 and developed in collaboration with efabless, has also been manufactured and will be released soon.

For more information contact Antmicro at contact@antmicro.com or zGlue at info@zglue.com.