Adelsbach Math Vector Library

Organization: Adelsbach UG

The Adelsbach Math Vector Library is an accelerated high-performance vectorized mathematical function library.

License Type: Proprietary

Software Type: Librarires, Accelerated Libraries, Machine Learning, AI

Alibaba T-Head TH1520 SoC

Organization: BeagleBoard.org

BeagleV®-Ahead

License Type: Permissive

Software Type: Chips

Andes Technology Asus Tinker V

The first RISC-V single-board computer (SBC) from ASUS IoT embraces open-source architecture to expand options for industrial IoT developer community First ASUS IoT RISC-V SBC:64-bit processor embraces open-source RISC-V architecture to deepen diversity and flexibility for IoT developers Ideal for industrial IoT:Rich connectivity, assured longevity and reliable, trusted technical support Linux Debian and Yocto support:Accelerates adoption of RISC-V and deployment in industrial IoT applications

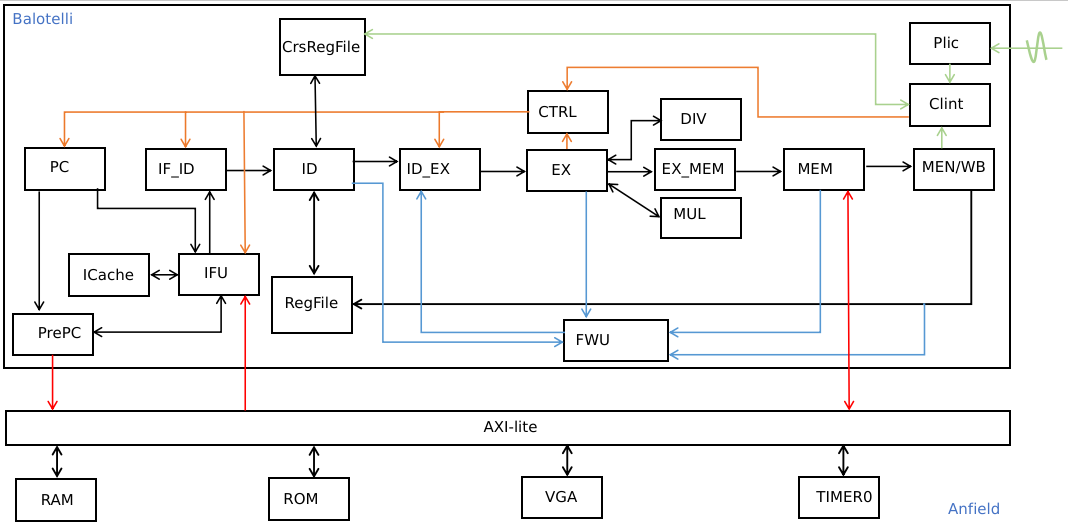

Anfield

Organization: Kai

An incomplete SoC

Software Type: Soft IP

Arabic course in Computer Architecture taught in RISC-V ISA

Organization: Umm Al-Qura University

An Arabic course in Computer Architecture taught in RISC-V ISA based on Computer Organization and Design the Hardware/Software Interface, RISC-V Edition, David Patterson and John Hennessy by Dr. Ghassan F. Bati. http://www.uqu.edu.sa/gfbati

License Type: Copyleft

Learn Language: Arabic

Aries M100PFS - System on Module based on PolarFire SoC FPGA (M100PFS-250BAABE-1 V1.3)

Organization: Aries Embedded GmbH

The M100PFS is based on the PolarFire SoC FPGA architecture by Microchip and combines high-performance 64-bit RISC-V cores with outstanding FPGA technology. The platform integrates a hardened real-time, Linux capable, RISC-V-based MPU subsystem on the mid-range PolarFire FPGA family, bringing low power consumption, thermal efficiency and defence grade security to embedded systems.

Aries M100PFS-250BAAB-1

Organization: Aries Embedded GmbH

The M100PFS is based on the PolarFire SoC FPGA architecture by Microchip and combines high-performance 64-bit RISC-V cores with outstanding FPGA technology. The platform integrates a hardened real-time, Linux capable, RISC-V-based MPU subsystem on the mid-range PolarFire FPGA family, bringing low power consumption, thermal efficiency and defence grade security to embedded systems. The RISC-V CPU micro-architecture implementation is a simple 5 stage, single issue, in-order pipeline that doesn’t suffer from the Meltdown and Spectre exploits found in common out-of-order machines. All five CPU cores are coherent with the memory subsystem allowing a versatile mix of deterministic real time systems and Linux in a single multi-core CPU cluster.

ARIES V2.0

Organization: Centre for Development of Advanced Computing

The ARIES v2.0 is a fully indigenous and a “Made in India” product to get started with basic microprocessor programming and embedded systems. This board is built upon a RISC-V ISA compliant VEGA Processor with easy-to-use hardware and software. The VEGA SDK also provides full ecosystem with numerous examples and support documentation.

License Type: Proprietary

BBC Doctor Who HiFive Inventor Coding Kit

Organization: SiFive

Doctor Who takes coding to the next level with the revolutionary HiFive. BBC/Tynker coding is a combination of the best in entertainment with the best in technology for learning. Using play and stories to enable learning is a long-established practice among educators. Using the Doctor Who story to inspire learners to code using the well-respected Tynker coding environment means that children learn in a non-threatening yet challenging environment that encourages success and learning through play. Uses Cases include Internet of Things (IoT), learning computer programming, artificial intelligence, robotics, and more! Features SiFive RISC-V FE310-G003 processor

BeagleBoard - BeagleV®-Ahead

Organization: BeagleBoard.org Foundation

BeagleV®-Ahead is an open-source RISC-V single board computer (SBC) in the form factor of BeagleBone Black with compatible P8 & P9 cape header pins allowing you to stack your favorite BeagleBone cape on top to expand it’s capability. Featuring a powerful quad-core RISC-V processor, BeagleV®-Ahead is designed as an affordable RISC-V enabled pocket-size computer for anybody who want’s to dive deep into the new RISC-V ISA. Use Cases include rapid prototyping of low-power, low-latency embedded systems, rapid prototyping of RISC-V SoC designs and industrial automation. Features Microchip PolarFire® MPFS025T quad-core RISC-V System on Chip (SoC) with FPGA fabric and management CPU subsystem, 2GB LPDDR4 memory, 16GB Kingston eMMC flash memory, Gigabit Ethernet, 2x46 pin BeagleBone compatible headers, E-Key M.2 socket for WiFi modules, High-speed SYZYGY connector, CSI connector compatible with BeagleBone AI-64, microSD socket