Two meetings hosted on Wednesday May 6 to learn about Multicore RISC-V Designs in AI & Machine Learning Applications

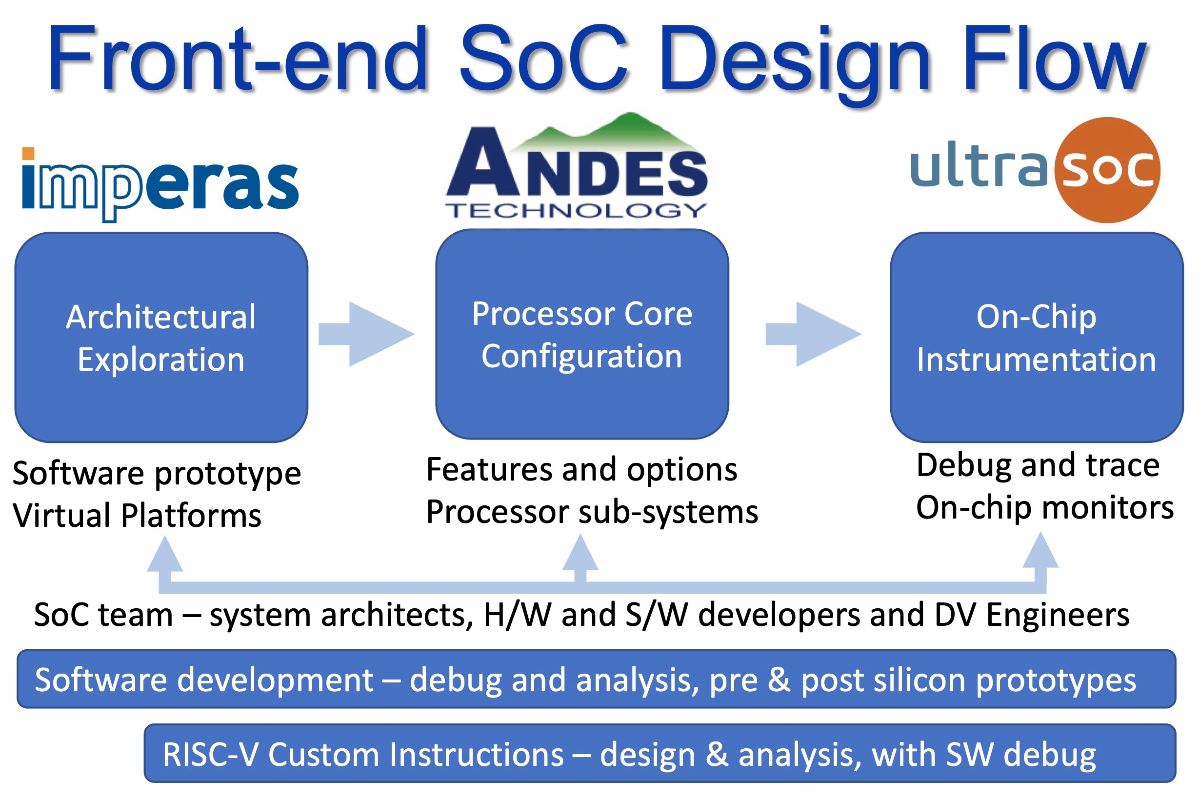

Imperas, Andes, and UltraSoC invite SoC designers developing next generation devices to learn how to better optimize, test, and evaluate multicore RISC-V designs for AI inferencing and machine learning applications.This webinar covers the latest challenges being faced by designers when migrating AI/ML applications to custom SoCs with RISC-V to accelerate complex algorithms and applications. While highlighting new application examples, many of the techniques and insights can equally be applied to any RISC-V based SoC design.This webinar will cover the key SoC design stages of:- Architectural exploration – Software driven prototype analysis with virtual platforms

- RISC-V core configuration – Optimized features for cores and processor sub-systems

- Full on-chip instrumentation – Debug and trace, and on-chip performance monitors

The webinar will be hosted by Mike Ingster, President and Founder of Quantum Leap Solutions (QLS), and will conclude with a Q&A session with the presenters. “Moving an SoC solution from proof-of-concept to prototype stage and into volume production requires close alignment of multiple tools, techniques and methodologies to achieve first pass silicon success. RISC-V offers designers greater freedom and opportunities. And by leveraging the expertise of partners Imperas, Andes and UltraSoC, RISC-V designs can deliver a faster time to market.”

Imperas Software, the leader in virtual platforms and high-performance software simulation, will highlight the experience of profiling and architectural exploration using virtual platforms to model the design trade-off for compute resources with full software workloads for AI/ML.

Andes Technology, a leading supplier of high efficiency, low-power 32/64-bit RISC-V processor cores, will cover the details of selecting the correct IP core options and configurations to support complex SoC design implemented with leading commercial EDA tools and flows.

UltraSoC Technologies, a leading supplier of on-chip instrumentation IP for analysis and monitoring many-core SoC designs, will illustrate the key requirement to instrument many-core SoC designs anticipating the requirement for software debug during development and remote monitoring in deployment as part of the front-end design of the SoC.

Webinar: Multicore RISC-V Designs in AI & Machine Learning Applications

Held on Wednesday May 6th 2020

With two meeting time slots available to choose from:

Meeting at 8am (PDT) or 5pm (PDT)

City comparisons:

San Jose: 8am (PDT) or 5pm (PDT)

London: 4pm (BST) or 1am (BST on May 7th)

Paris: 5pm (CET) or 2am (CET on May 7th)

Bangalore: 8:30pm (IST) or 5:30am (IST on May 7th)

Taipei: 11pm (CST) or 8am (CST on May 7th)

Book your seat:

]]>