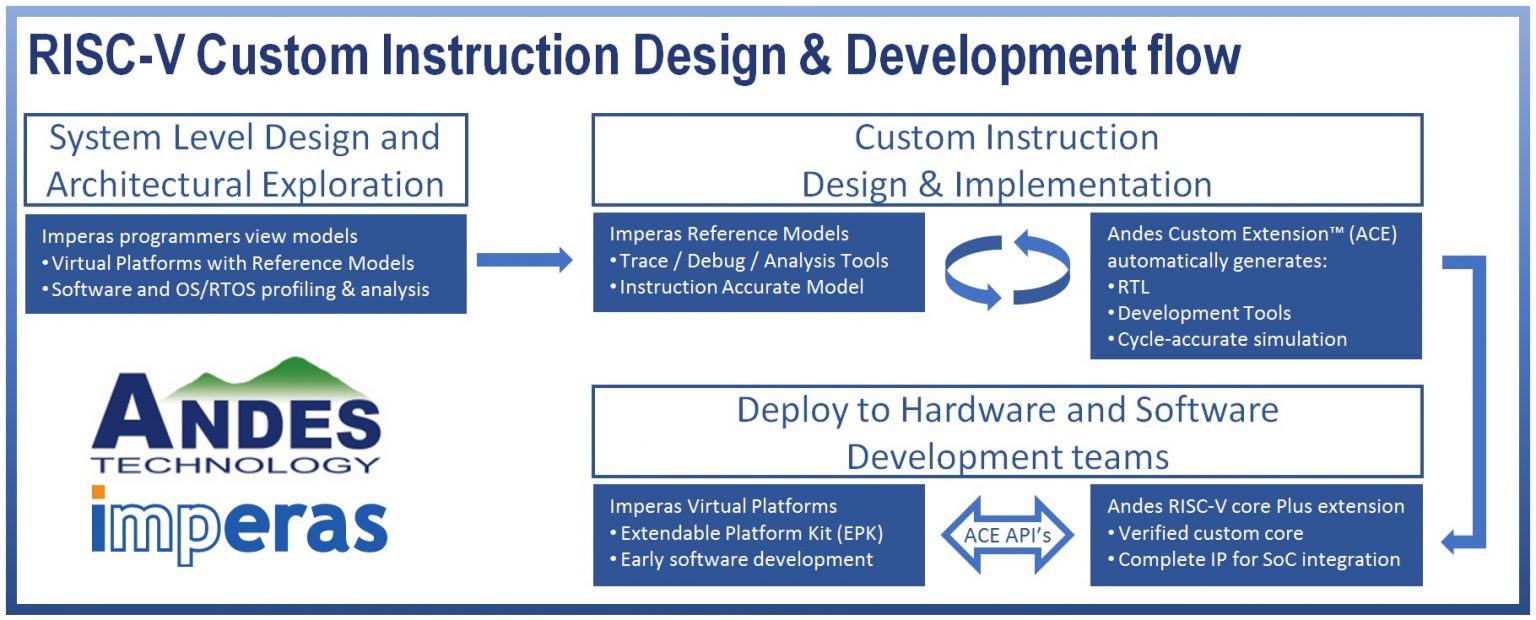

HSINCHU, TAIWAN AND OXFORD, UK – December 03, 2020 – Andes Technology Corp., a leading supplier of performance-efficient and extensible 32/64-bit RISC-V CPU cores and a Founding Premier member of the RISC-V International Association, and Imperas Software Ltd., a leader in high-performance software simulation and virtual platforms, announced today to extend their cooperation to the versatile Andes Custom Extension™ (ACE) and Imperas’ fast simulators. The joint work enables SoC design teams using the ACE framework to co-design hardware and software so that full software development can start before the silicon is available. Under the ACE framework, SoC designers can easily and efficiently define new instructions on the Andes RISC-V processor core to speed up target applications by writing ACE scripts for instruction semantics and concise Verilog for instruction execution RTL. Taking them as inputs, the powerful tool COPILOT (Custom-OPtimized Instruction deveLOpment Tools) automatically generates all required components to extend the existing Andes processor package, including the processor RTL, the compilation tools, the debugger and the cycle-accurate simulator, to support the new instructions. Read the full press release.[/vc_column_text][/vc_column][/vc_row]]]>