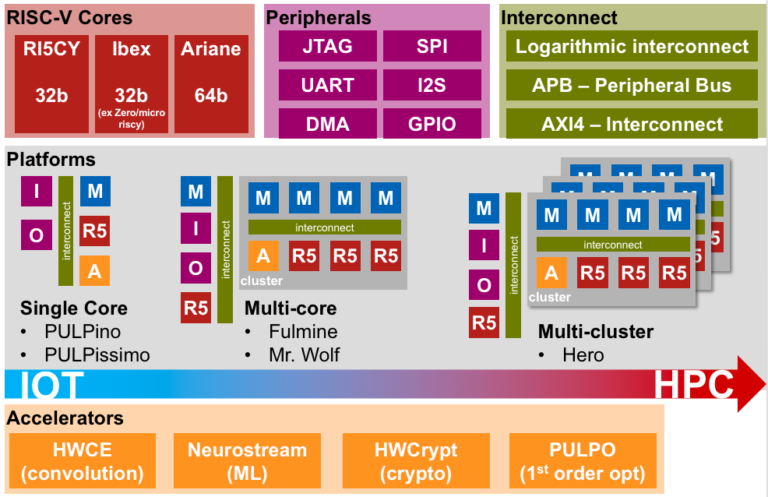

PULP Platform The Parallel Ultra Low Power (PULP) Platform started as a joint effort between the Integrated Systems Laboratory (IIS) of ETH Zürich and the Energy-Efficient Embedded Systems (EEES) group of the University of Bologna to explore new and efficient architectures for ultra-low-power processing. Read the full article[/vc_column_text][/vc_column][/vc_row]]]>