Pixilica in the US has worked with the RV64X to propose a new set of graphics instructions designed for 3D graphics and media processing in a fused CPU-GPU ISA, creating an open source reference implementation for FPGAs.

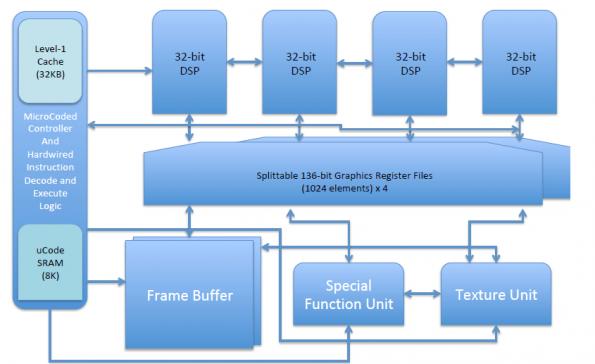

The RV64X Reference Implementation includes an Instruction/Data SRAM Cache (32KB), a Microcode SRAM(8KB), a Dual Function Instruction Decoder, an Hardwired implementing RV32V and X, a Micro-coded Instruction Decoder for custom ISA, a Quad Vector ALU (32 bits/ALU – fixed/float), a 136-bit Register Files (1K elements), a Special Function Unit, a Texture Unit, and a Configurable local Frame Buffer.