I attended the RISC-V Global Forum on September 3, 2020. I must say, the pandemic does not deter the progress of the global RISC-V community in innovating, collaborating and exhibiting their work. I am Shivam Potdar, a senior EE undergraduate from the National Institute of Technology Karnataka, India. I got introduced to RISC-V about a year ago through the course content of CS61C, UC Berkeley. I then got an opportunity, as a Google Summer of Code (GSoC) student with the Free and Open Source Silicon Foundation (FOSSi), to explore several novel technologies, which, coupled with RISC-V, are set to shape the future of our industry. Now it has turned into a never-ending journey for knowledge and exploration. GSoC is a program funded by Google to encourage students to contribute to open-source projects. Thanks to the inception of RISC-V and organizations like FOSSi, lowRISC, Symbiflow, BeagleBoard.org, etc., open-source hardware projects are seeing increasing involvement. One of the most exciting aspects of RISC-V is that it provides an open playground for new ideas across multiple domains. It has become the go-to for architectural innovations like OpenTitan and for exhibiting new HDLs like Chisel (Rocket chip, SiFive cores), SpinalHDL (VexRiscv), BlueSpec (Shakti processors), etc. I was able to make the most of a summer of mandated isolation by exploring:

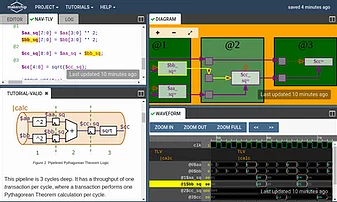

- transaction-level modeling with TL-Verilog

- easy design and debug with Makerchip

- open-source hardware and freely available design tools

- open source formal verification

- a heterogeneous ISA manycore platform