The RISC-V ISA (Instruction Set Architecture) permits a range of possibilities for processor implementation with a modular approach for standard and custom extensions. In addition, implementations may be shared commercially or as open-source, and adopters beyond the original design team can use these directly or as a basis for further modifications and enhancements.

The OpenHW Group is a not-for-profit, global organization of members based on the principles of open-source hardware IP, with full commercial grade standards for delivery and quality. The initial processor designs originated within the PULP platform at the University of Bologna and ETH Zurich under the guidance of Professor Luca Benini. These early RISC-V implementations became well known within the RISC-V community and soon attracted interest from a wide range of SoC early adopters. The delivery of trusted and reliable semiconductor IP depends on many aspects, from software ecosystem support and core features to verification and quality. The first step is to address the verification aspects and the flows adopted by the OpenHW Group Verification Task Group, based on leading industry best practices with commercial tools.

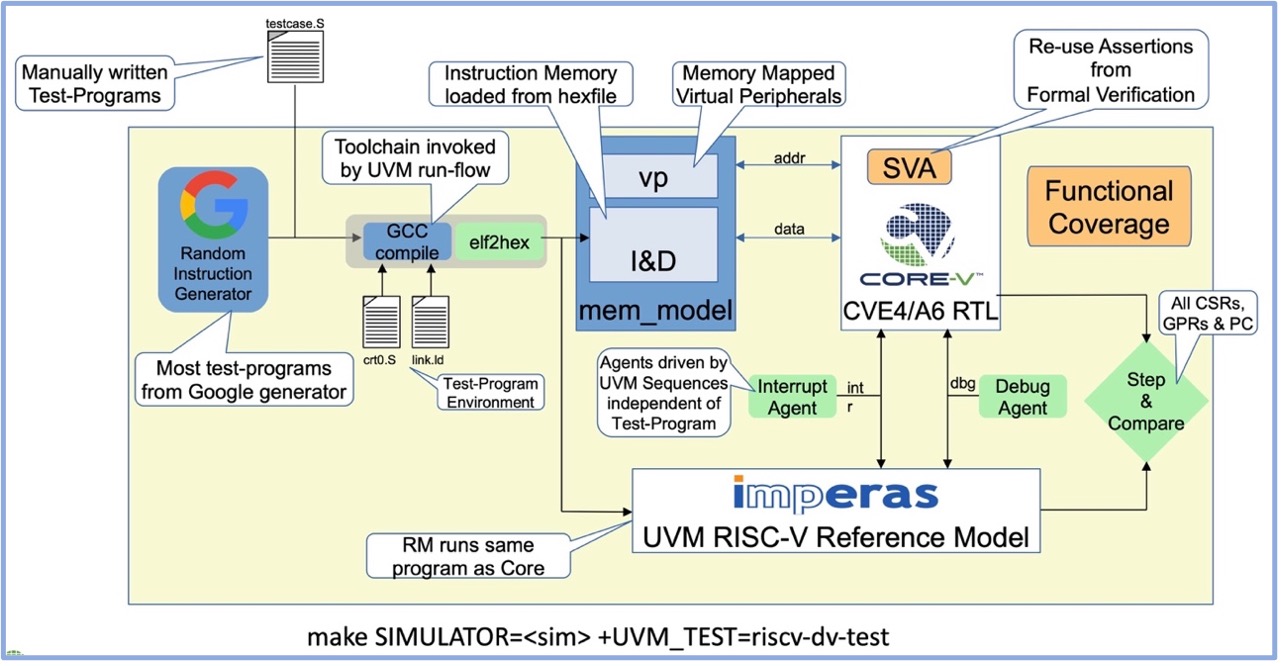

To help and support SoC design teams looking to adopt CORE-V, the OpenHW Group has established several working groups to address the key areas of IP development, ecosystem tools and developer resources. To address the typical concerns of quality and usability of open source hardware IP, the OpenHW Group Verification Task Group has published the complete verification test plan. See the diagram below. Also to ensure the smooth adoption within the current SoC designs flows, the DV plan is based on industry best practices and leading commercial tools. To support adopters looking to further modify or extend the designs, all the scripts and test files are also made available.

Diagram to show the OpenHW CORE-V verification test bench UVM environment.

A test plan represents not just the operational steps to complete the test and verification tasks but is also a fundamental reflection of the quality of the final deliverables. Any deficiencies or oversights in the test plan may result in defects remaining in the final products. In traditional commercial activities, the test plans and tests cases are considered as highly valued IP and not shared externally with customers or users, in fact the test methodology itself is regarded as a strategic competitive advantage. As open-source processor IP, the CORE-V deliverables can be used as-is or as a basis for further design modifications and enhancements. Thus, the complete OpenHW CORE-V test plan and test bench is provided to help support adopters, and may be used to help and assist in developing SoC level tests.

The Imperas reference model covers the complete envelope of the RISC-V specification including user and privilege modes. To support processor verification, the Imperas reference model is encapsulated within SystemVerilog for test benches to compare the RTL against the reference model. The test bench also supports a step-and-compare approach which allows interactive debugging to help investigate resolve issues. In automated regression tests, the reference model can be set-up to cover implementation options across the entire range of processor feature sets and options. The configuration flexibility is just one of the many differences between IP verification and adopters DV plans for a targeted implementation within an SoC or FPGA designs.

To support the team effort across multiple geographical locations and corporate members, the OpenHW Verification Working Group has leveraged the cloud-based EDA platform of Metrics Technologies. The Metrics cloud-based methodology supports both collaboration across the team members, but also the intensive compute resources required for extensive processor verification. Using a cloud-based infrastructure permits a flexible approach to the simulation capacity which can scale from the initial set-up of test cases to running the extensive verification tasks. As the group can share results, coverage and log files within the platform, it greatly helps both the communications across the distributed team and helps maintain a clear record of all results as key milestones on coverage are achieved. A recent paper estimated that simulation of 1015 (peta) instructions as a guide to the capacity that is required for processor IP verification.

The OpenHW Group members are actively developing the CORE-V processor IP, verification and ecosystem support for SoC adopters. To learn more about the OpenHW Group and all the contributions from the supporting members please visit https://www.openhwgroup.org

Kevin McDermott

VP Marketing, Imperas Software and co-lead of OpenHW Marketing Working Group