Support for co-simulating HDL models in Renode with Verilator has been an integral part of the framework since the 1.7.1 release, introducing a new dimension of flexibility and allowing Renode to cover ASIC and FPGA SoC development use cases. Renode is a versatile simulation framework that allows you to easily run unmodified software inside simulated environments composed of highly-reusable building blocks representing components of a platform; co-simulation allows you to attach an externally created peripheral, e.g., built with Verilog to a Renode simulation to function as any other part of the simulated system. This allows you to iterate your hardware RTL development while benefiting from the infrastructure, feature set, and speed of Renode running the rest of the system on a functional level. Thanks to recent developments for our customers interested in even more control over their simulated environment driven by the needs of advanced RISC-V silicon development, support for Verilator in Renode has been expanded to allow CPUs simulated directly from RTL, which opens an array of new possibilities for developing new CPU core IP and combining it with Renode’s vast portfolio of peripheral IP for a complete system able to run advanced software.

Support for RTL CPUs in Renode

To this moment, the Verilator integration in Renode focused mostly on peripherals like UARTs, various types of memory, CFUs (Custom Function Units), or DMA (Direct Access Media) controllers but the “brain” of the simulation was a Renode-based CPU that accessed those peripherals by reading/writing from/to registers via the system bus. While previously developed HDL components provided some level of interactivity, like UART reacting on input and generating an interrupt or DMA initiating a transfer on a bus, the verilated CPU takes it to a whole new level of complexity.

Since the CPU is the main driving force in the embedded system simulator, enabling the simulation of a CPU directly from RTL required adjusting the abstract APIs in Renode to allow external CPUs. Until now, the default way of simulating a CPU was using Renode’s translation library (tlib) implemented in C, but the new improvements open a possibility for easier integration with any type of external CPU simulator. Adding this functionality also required the Renode-Verilator integration library to be extended to support a new type of component. It also necessitated support for HDL peripherals to initiate transactions on Wishbone and AXI buses. If you want to delve deeper into Verilator peripherals in Renode, visit renode-verilator-integration repository on GitHub to see and build a wide range of sample peripherals.

Adding a RTL CPU to your project

Each component in any Renode project is a separate building block, representing CPUs of different architectures and a wide range of communication buses and interfaces. The modular nature of Renode allows you to modify any platform easily and include new blocks by changing only a few lines in existing `.repl` files, making it easy to experiment with the simulated platform.

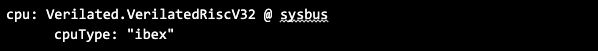

To add an RTL CPU model, e.g., OpenTitan’s Ibex RISC-V implementation, to the description of your own platform in Renode, you will need to create a block representing the CPU and declare its type:

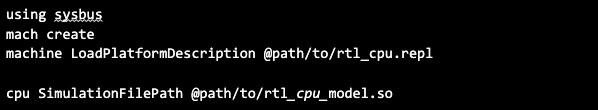

Then you can edit your .resc script to load the library of the RTL CPU from the chosen location:

The simplicity with which you can switch between regular and RTL CPU models lets you either experiment with mixed setups where some cores are simulated directly in Renode, and others are attached externally or compare the execution of different CPU implementations using the gdb-compare script.

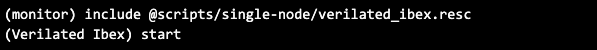

If you want to see the RTL CPU in action on your local machine, load the verilated_ibex script and start the simulation:

Simulate complex systems for software-driven ASIC development

Renode is a flexible tool that can be used to simulate various complex scenarios, including co-simulation with external simulators like Verilator for development of new silicon. The modularity of Renode platforms makes them easy to integrate into existing workflows and toolchains, allowing your projects to benefit from having a reliable and deterministic simulation environment, all open source. If you are interested in commercial support in building your custom platforms in Renode or enabling new features, use cases, and integrations, reach out to Antmicro at contact@antmicro.com.