Since 20 years ago, Intel has successfully developed the 3 GHz processor in 130nm process. However, as the design complexity of IC continues to increase, so does the demand on EDA flow.

- Background

Traditional fabrication methods often require large margins to ensure functional performance, But the adoption of public tool chains and open PDK can recycle these margins by the wisdom of the masses. Because, EDA licenses will no longer serve as a bottleneck to design space exploration in this field.

Therefore, we are trying to answer whether the open EDA tools are competent for building a modern processor? What’s the gap between open and proprietary ASIC fabrication flow? That’s why we build GreenRio, a RISC-V core with modern processors characteristics.

Through building such non-toy-like design, we optimized the OpenEDA along with the RISC-V architecture together and explore every stage of this flow.

- GreenRio Development History

Figure 1 Milestone of GreenRio

GreenRio1.0 is a 7-stage, dual-issue, out-of-order (OoO) processor. We demonstrated it in the efabless OpenMPW-7 program using the Skywater 130nm process. Related works were accepted by the Workshop on Open-Source EDA Technology (WOSET) as well as RISC-V Days Tokyo 2022 Autumn2. Greenrio 2.0 adds more hardware supports allowing for running applications. GreenRio2.0 has won the ISSCC Code-a-Chip competition and is becoming a benchmark in the OpenEDA domain.

- User Experience of Open Toolchains

One of the challenges that the community faces is the gap between open and proprietary tools in terms of QoR and runtime. So We quantified this gap by hardening GreenRio. We used open EDA Tools: OpenROAD/OpenLANE versus appropriate EDA tools: Genus/Design Compiler/Innovus to harden this design.

We can concluded that:

- The open pdk lack of process corners and key parameters for timing optimization, also exists bugs

- Compared to propriety tools, the open one is not complete enough and needs further optimization

- For logic synthesis, propriety tools bring about smaller area, less gate count and lower leakage power. But the open tools win in synthesis time and can get time convergence netlists without human adjustment.

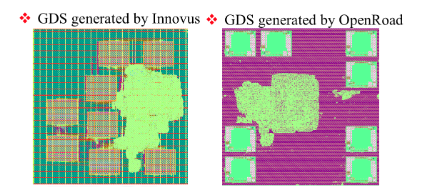

- For physical implementation, compared to Innovus, open tools cannot achieve higher core utilization and higher cell density. Currently, it is inferior in both runtime and performance, because its placement/routing engines are out-of-date.

- For the runtime allocation, open tools spend most of the time in routing, but the other one puts more effort in placement.

Figure 2 Different macro placement

- Design Space Exploration in RISC-V Chips and OpenEDA

The design complexity of GreenRio has revealed the convergence difficulty in the Open-Chip flow. Designs and fabrications flows complement each other and grow together. Just as the open source compilers GCC/Clang, they have revolutionized the software development industry. The optimization capabilities in Open toolchains also has the potential to transform the hardware landscape

we believe we can customize chips with small amount of work in future. We can leverage the power of open-source community to collectively push the frontiers of hardware innovation. Our lab will keep iterating GreenRio, keep narrowing the gap between open and proprietary back-end softwares.

Think about ChatGPT in NLP field, ultimately, we may realize using machine to develop architectures.