The Box64 RISC-V backend has implemented scalar instructions to emulate x86_64 vector extensions like MMX and SSE*, ensuring good compatibility with the rv64gc architecture. However, vector instructions often require dozens of scalar instructions for accurate emulation, leading to significant performance overhead in x86_64 applications that heavily rely on vector instructions.

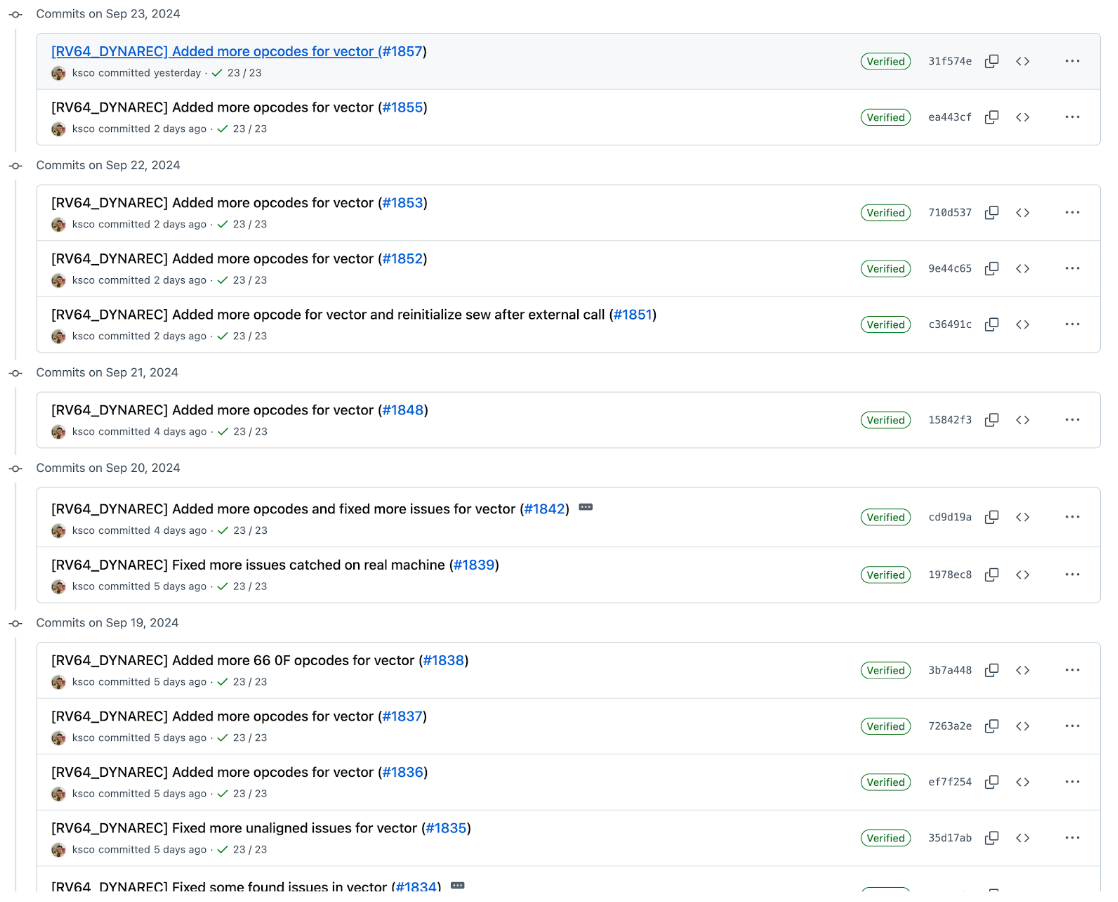

Recently, developers from the PLCT Lab added preliminary support for RVV 1.0 to the Box64 RISC-V backend, submitting more than 30 Pull Requests. Currently, the Box64 RISC-V backend has now reached the level of efficiently translating over a hundred SSE instructions into RVV instructions.

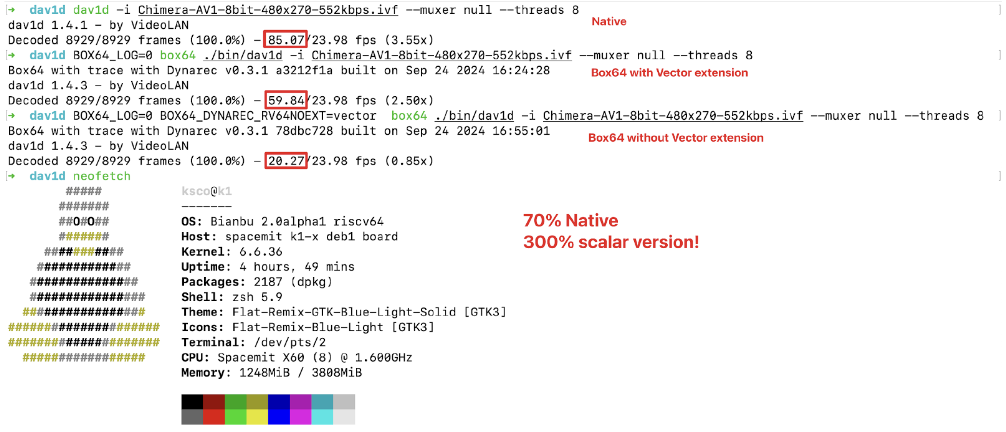

The new Box64 RISC-V backend was tested on the SpacemiT K1 board (8 cores, RVV 1.0, VLEN 256), measuring performance while running dav1d, as shown in the graph below.

dav1d is a well-known cross-platform open-source AV1 video decoder, with its x86_64 version making extensive use of SSE instructions. By translating SSE instructions into RVV instructions, Box64 significantly reduces the performance overhead associated with binary translation. As shown in the graph, with V extension support enabled, performance reached 70% of native execution, marking a 300% improvement over the scalar version!

Please note that the significant performance boost observed with dav1d is due to its extensive use of SSE instructions in hot code, and these results may not be representative for all workloads. The extent of performance improvement can vary from one program to another, necessitating a detailed analysis.

PLCT Lab will continue to enhance Box64’s support for RVV 1.0 and welcome developers worldwide to contribute to the RISC-V software ecosystem!