By: Nick Brown, EPCC

High Performance Computing (HPC) is one of the most exciting and challenging fields, solving the world’s biggest problems with incredible levels of processing power.

With an ever-present demand for greater performance, at the same time as increased focus on improving the sustainability of operations, the High Performance Computing (HPC) community is facing new challenges in delivering what is demanded of them by users and society. The RISC-V ISA has the potential to answer these challenges and is gathering momentum within the HPC community. The flexibility provided by RISC-V, where more specialized solutions can be developed, will help address some of the performance and energy bottlenecks that until now have been insurmountable while HPC relies on commodity parts.

Growing interest in the use of RISC-V within the HPC community is in part, due to the series of highly successful workshops, panels, and collaborative sessions that have been organized by the RISC-V HPC Special Interest Group (SIG) at world-leading HPC conferences in the past few years.

In this blog we will outline a series of very successful events last November at SC24, and how you can ride this momentum by joining us at ISC25, where the call for papers has just opened with a deadline of 16th of March (AoE).

RISC-V for HPC workshop at SC24

Every November the HPC community descends on a major American city to take part in SC. With a mixture of academic papers, workshops, panels, and a large exhibition filled full of vendors, this is the largest HPC conference in the calendar and last year’s event set a record with over 18,000 participants.

The RISC-V HPC SIG organized two events at SC; a workshop on RISC-V for HPC and a panel. In 2023, our RISC-V workshop at SC filled the room out so there are high hopes for this year’sinstallment. The workshop began with Dave Ditzel, founder and CTO at Esperanto Technologies, discussing his journey with RISC before focusing on why he chose RISC-V for Esperanto and describing their current and future AI and HPC accelerators. It was especially interesting that the next generation of their product, the ET-SoC-2x will have full accelerated support for FP64 (which is important in HPC) and Dave forecasted that around 36 racks of that hardware will deliver around an exaflop of FP64 performance.

This was then followed by vendor lightning talks by Inspire Semiconductor, Tenstorrent, and E4 Computer Engineering. In 2023, these vendor talks were popular as they provided the audience with insights into hardware that is shipping today and in the near future. Inspire Semiconductor plans to ship their Thunderbird PCIe accelerator card in 2025 which is designed from the ground up for HPC, Tenstorrent already has their Grayskull and Wormhole cards available for purchase with further generations available next year, and E4 Computer Engineering has a range of interests in RISC-V including a dual-socket SG2042 workstation.

Research papers, where members of the community present their latest work on RISC-V for HPC were also a key part of the workshop. Five papers were presented in total, and these included talks from using the Tenstorrent Grayskull for accelerating stencil codes to exploring the vectorization and performance of an astrophysics application on RISC-V with HPX and Kokko, to a web-based simulator for RISC-V superscalar processors that is especially useful in teaching.

It was a packed session, finished off by Jeff Scheel, Director of Technical Programs at RISC-V International, giving the organization’s perspective on HPC, describing the wider ecosystem, where they see HPC fitting in, and how people can get involved. Full details of the workshop, as well as many of the slides, are available at https://riscv.epcc.ed.ac.uk/community/workshops/sc24-workshop/.

RISC-V panel at SC24

To create more of an opportunity to have a free-flowing discussion between the RISC-V experts and the audience, the HPC SIG also hosted a 90-minute panel discussion session in the main SC technical program. Chaired by Nick Brown (EPCC at the University of Edinburgh) and with expert panelists Dave Ditzel (Esperanto Technologies), Jeff Scheel (RISC-V International), Doug Norton (Inspire Semiconductor), Teresa Cervero García (Barcelona Supercomputing Centre) and Eric Duffy (Tenstorrent), there was a deep and wide range of expertise to draw from.

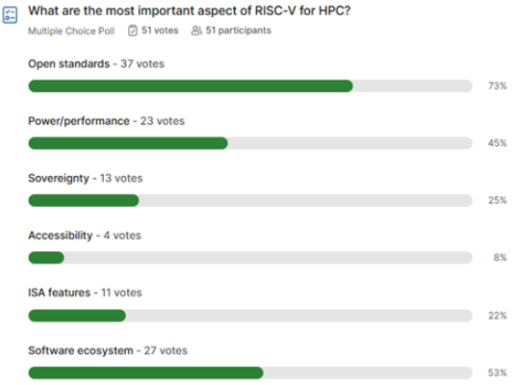

Similarly to the session at ISC24, the session started off by asking the audience to vote on what they felt were the most important aspects of RISC-V for HPC, and once again “open standards” was the most popular answer. This was a surprise at ISC, and the fact that the audience had the same answer demonstrates that the HPC community has taken on board the benefits of the openness provided by RISC-V. But there were also some differences in this answer, for instance at ISC, power and performance came a close second, whereas at SC the software ecosystem was voted more important.

Many different topics were discussed during the panel including impressions that there are a very large number of extensions being added to the specification and how sustainable this is in the future, whether mixing and matching parts of the ISA can impact code portability, whether there is best practice for developing RISC-V code to help ensure it is future proof, and whether there are downsides to community-driven development of standards and technologies.

Such a discussion is very useful, not only to explore, unpack, and educate the audience on the specific points being raised but also the questions themselves help demonstrate the HPC community’s current understanding and concerns around RISC-V, enabling us as the SIG to identify areas which we can improve messaging on.

A very successful RISC-V at SC24

In addition to the formal RISC-V sessions at SC, there were also RISC-V vendors and technologies on the show floor showing how they were making RISC-V a real part of HPC centres. For instance, Penguin Computing had an Esperanto ET-SoC-1 on their booth and is selling a compute solution using this technology, Tenstorrent had a presence on the show floor and ran a networking event one evening, while E4 Computer Engineering had a booth and experts who could speak about RISC-V to interested attendees. Furthermore, Barcelona Supercomputing Centre had a demo of a RISC-V system at their booth which was running a Computational Fluid Dynamics (CFD) code and demonstrating Fortran and QEMU support.

The RISC-V workshop at SC24 was a great success, with HPCWire featuring RISC-V in their observations of SC article (https://www.hpcwire.com/2024/11/21/sc24-observations-china-politics-risc-v-and-cxl/) focusing in on the points made by Dave Ditzel in his workshop keynote about chiplets.

You can join in with the momentum displayed for RISC-V in HPC at SC24 by joining us at ISC25!

ISC25 Call for Papers

We are holding a workshop on RISC-V for HPC at ISC25 (Europe’s largest HPC conference) on the 13th of June 2025 in Hamburg, and the call for papers is open now. We welcome the submission of both mature and work-in-progress activities, with accepted papers published in the Springer workshop proceedings. The deadline for paper submission is the 16th of March (AoE) and more details can be found at https://riscv.epcc.ed.ac.uk/community/workshops/isc25-workshop/

We hope to see you there!