The knowledge gap for porting software to RISC-V is about to close.

RISCstar Solutions, in close collaboration with RISC-V International and the Linux Foundation, has developed a comprehensive online training course designed to help developers port and optimize code for RISC-V from other major RISC architectures. The course will be available worldwide, free of charge.

This isn’t a basic introduction — it’s a hands-on, practical guide created by engineers who work deeply with RISC-V every day. The program was led by Daniel Thompson of RISCstar, with contributions from experienced developers including Wei Fu from Red Hat and others who brought their real-world insight and deep cross-architecture expertise to the material.

The result is a rich, technically grounded course that empowers developers to confidently migrate, optimize, and innovate on the RISC-V platform.

Why this training course matters

RISC-V International chose to work with RISCstar to create this training for a reason: their RISCstar Solutions team has mastered dual expertise in both RISC-V and other major SoC platforms. This cross-architecture fluency is exactly what you need when porting real-world applications.

The course delivers:

- Systematic approaches to code migration and optimization from industry veterans

- Architecture comparison insights that only come from engineers who’ve worked across multiple platforms

- Practical techniques proven in production environments, not just theoretical exercises

- Clear pathways from other ISAs to high-performance RISC-V implementations

Accelerate your transition to open architectures with this hands-on course designed to help you port and optimize software from other architectures to RISC-V. Explore key architectural differences, master instruction set nuances between A64 (Armv8.0) and RV64GC, and learn how to adapt assembly and SIMD-optimized C/C++ code for RISC-V platforms. You’ll also cover OS support, memory models, and system integration techniques essential for real-world deployment. Whether you’re optimizing existing code or expanding into RISC-V development, this course gives you the tools to bridge architectures with confidence and efficiency.

The course is in its final preparation stages and launching soon. Sign up HERE to receive notification when it goes live.

Porting to RISC-V Vector Extension Workshop October 22nd Santa Clara

In the meantime accelerate your learning by joining Daniel Thompson from RISCstar for an intensive hands-on workshop about RISC-V Vector (RVV) extensions during the RISC-V Developer Workshop Day on October 22nd in Santa Clara.

The future of high-performance computing is vector-length agnostic — and it’s happening,

If you’re a developer working with compute-intensive applications, this is your chance to master one of the most transformative features in modern processor design: RISC-V Vector (RVV) extensions. This workshop goes beyond the fundamentals to give you practical, immediately applicable expertise.

Why RVV Changes Everything

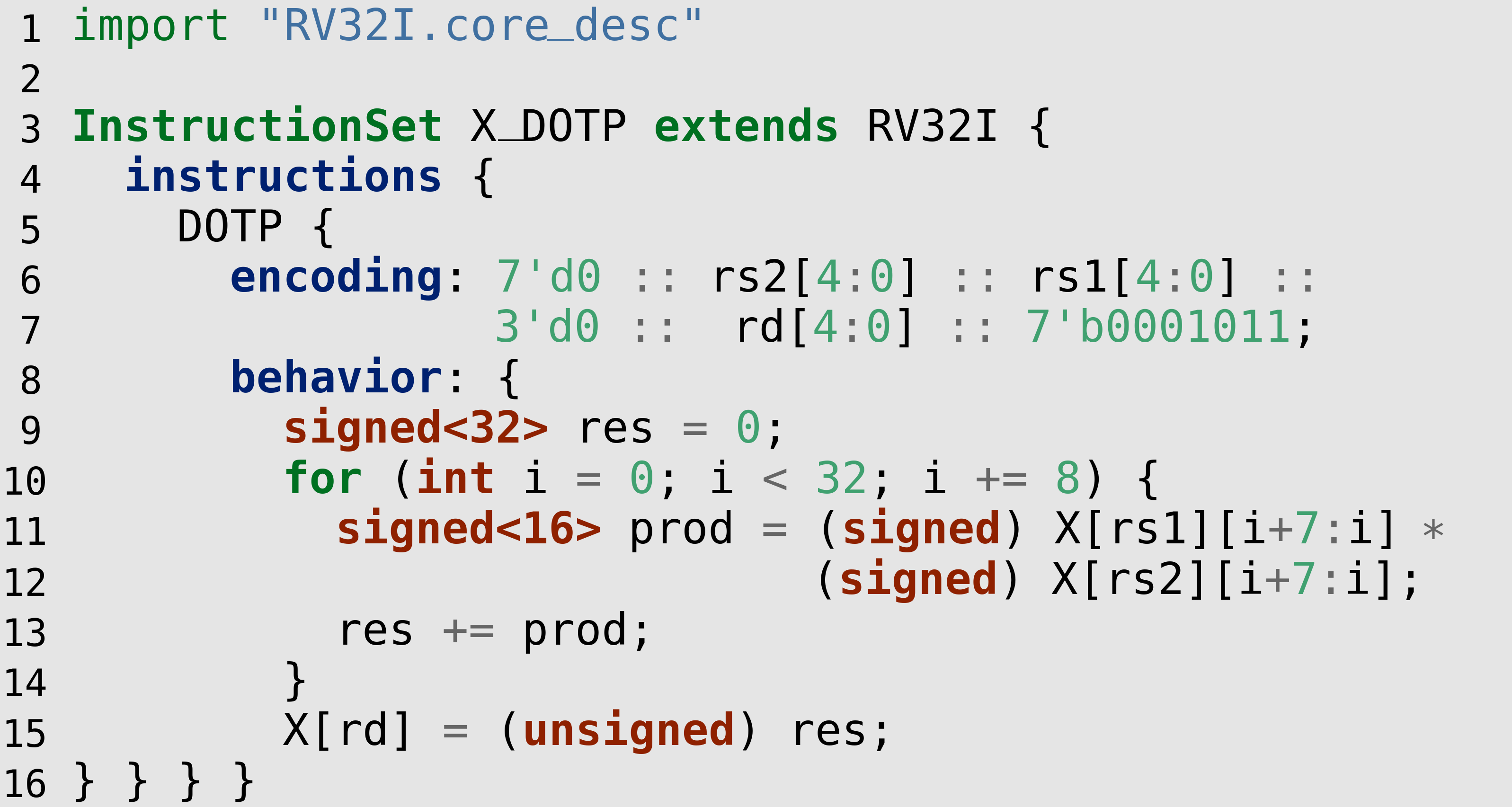

RISC-V Vector extensions aren’t just another SIMD implementation. They represent a fundamental rethinking of how processors handle parallel data operations — delivering unprecedented flexibility, scalability, and performance across machine learning, signal processing, cryptography, and beyond.

Unlike fixed-width vector architectures that lock you into specific hardware configurations, RVV’s vector-length agnostic (VLA) design means your code automatically adapts to different vector lengths. Write once, scale everywhere. This architectural elegance translates directly into performance gains and future-proof code that leverages new hardware capabilities without modification.

What You’ll Learn in This Intensive Workshop

- Core Concepts & Design Philosophy

Understand the architectural decisions that make RVV uniquely powerful, including the principles behind vector-length agnostic design and how it differs from traditional fixed-length SIMD approaches. - Real-World Code Migration Techniques

Move beyond documentation and dive into battle-tested strategies for converting optimized C code from other ISAs into high-performance RVV implementations. You’ll see exactly how experienced engineers approach this critical work. - Practical, Hands-On Experience

This isn’t a passive lecture. You’ll work through real examples, explore actual code transformations, and leave with techniques you can immediately apply to your own projects.

This Is Your Competitive Edge

As RISC-V adoption accelerates across cloud computing, edge devices, AI accelerators, and embedded systems, developers with RVV expertise will have a significant advantage. The ability to write high-performance vector code that scales across hardware implementations isn’t just valuable — it’s becoming essential.

Whether you’re optimizing machine learning inference, accelerating signal processing pipelines, implementing cryptographic operations, or pushing the boundaries of computational performance, mastering RVV opens new possibilities.

Next Steps

Don’t miss these opportunities. Sign up for the training course to get notified when it launches, and register for the October 22nd developer workshop in Santa Clara to accelerate your learning about RVV with hands-on guidance from industry experts.

The future of vector computing is vector-length agnostic. Make sure you’re ready for it.