Today’s RISC-V microcontrollers may lead to future RISC-V phones and laptops.

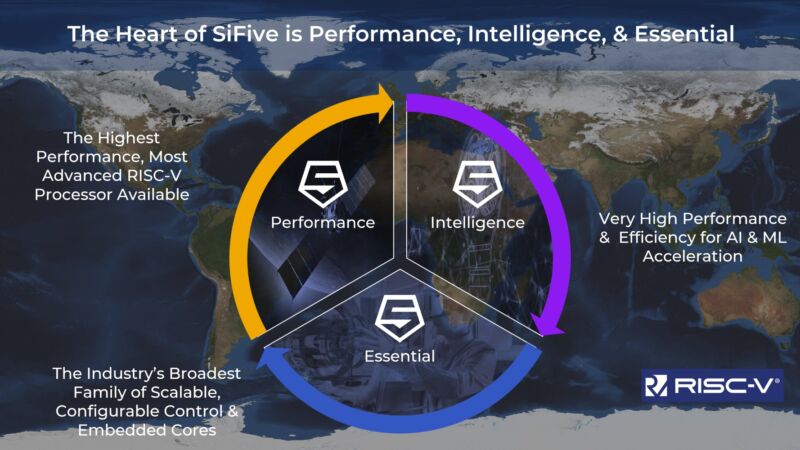

Today, RISC-V CPU design company SiFive launched a new processor family with two core designs: P270 (a Linux-capable CPU with full support for RISC-V’s vector extension 1.0 release candidate) and P550 (the highest-performing RISC-V CPU to date).

A quick RISC-V overview

For those not immediately familiar with RISC-V, it is a relatively new CPU architecture which takes advantage of Reduced Instruction Set Computer (RISC) principles. RISC-V is an open standard specifically designed to be forward-looking and evade as much legacy cruft as possible. One example of this design is RISC-V’s dynamic width vector instruction set, which allows developers to execute vector instructions on data of arbitrary size with maximum efficiency.