Box64 RISC-V 后端使用标量指令模拟实现了 MMX、SSE* 等 x86_64 向量扩展,实现了对于 rv64gc 的良好兼容性,但一条向量指令往往需要十几条甚至几十条标量指令才能模拟,因此,对于大量使用向量指令的 x86_64 程序,Box64 的性能损失相对较大。

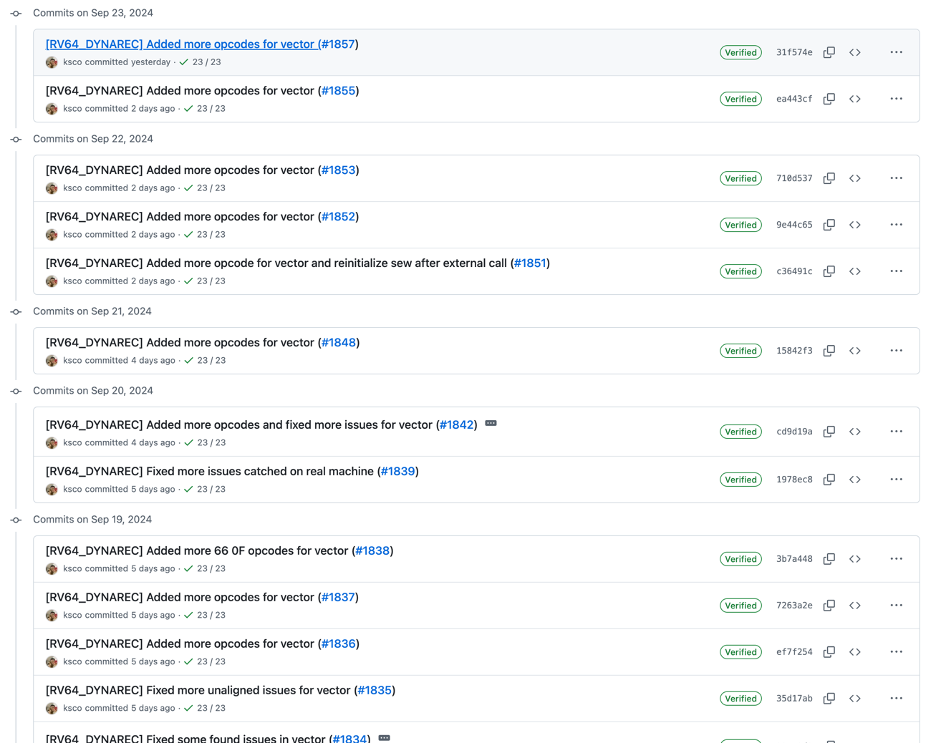

近日,来自 PLCT Lab 的开发人员为 Box64 RISC-V 后端新增了初步的 RVV 1.0 支持,提交相关 PR 30 余个,目前已经支持了百余条 SSE 指令到 RVV 指令的高效翻译。

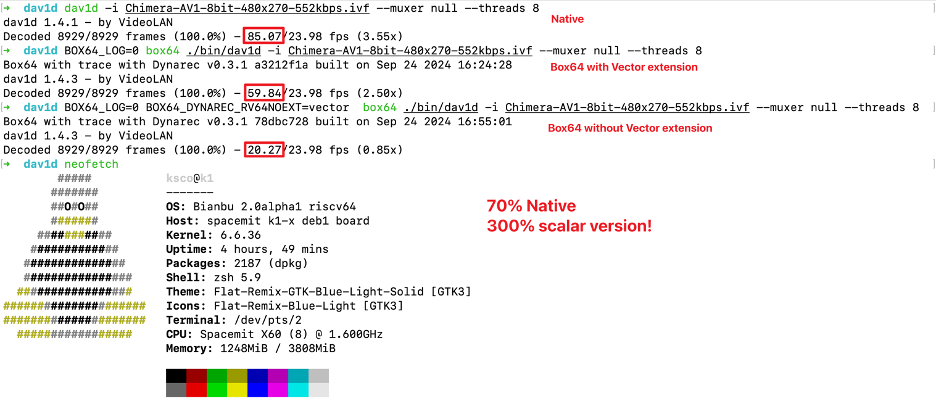

在 SpacemiT K1(8 核,RVV 1.0,VLEN 256)上,测试了新后端的在运行 dav1d 时的性能表现,如下图。

dav1d 是著名的跨平台开源 AV1 视频解码器,其 x86_64 版本大量使用了 SSE 指令。Box64 通过将 SSE 指令翻译为 RVV 指令,大大减少了二进制翻译的性能损失。从图中可以看到,开启了 V 扩展支持后性能评分达到了原生的 70%,达到了标量版本的 300%!

注意,dav1d 因为在热点代码中大量使用了 SSE 指令,因此测得性能提升较大,仅供参考,不具备普适性。每个程序的性能提升幅度不同,需要具体分析。

后续,PLCT Lab 将持续完善 Box64 RVV 1.0 的支持。欢迎全球开发者参与到RISC-V软件生态建设中来!