By Gadge Panesar, Chief Technology Officer of UltraSoC and Chair of the RISC-V Processor Trace Task Group For the last eighteen months, the RISC-V International Association Processor Trace Task Group has gone to great lengths to prioritize getting the RISC-V Processor Trace Specification polished and ready for the wider world. I’m proud to have chaired the Group, and to have witnessed the hard work we put in to get it done. The full announcement is available on the RISC-V International Association’s website. For those that want more details and to see the full list of RISC-V specifications, including Processor Trace, those are available to view here. Now that the processor trace specification has been ratified, we are able to offer a robust, highly efficient compressed standard to RISC-V developers and engineers. There is a consistently growing volume of support for RISC-V from all parts of the industry, with an increasing number of commercial implementations. We are witnessing new and exciting application areas opening up all the time. Why is trace so important? Well, depending on the project, somewhere between 50 and 75 percent of software development time is typically spent getting it to work – that’s debugging and integration. The workload gets much worse for increasingly complex systems where understanding the behavior of the whole system becomes very difficult. A key element of this process is the ability to have processor trace. As the name suggests, processor trace allows engineers to see exactly what instructions the processor core is executing, step by step. Ultimately, it means less time and fewer headaches for those working with RISC-V. Given how time consuming the task of debugging and integrating tools and extensions can be, the importance of a reliable processor trace is clear. It’s vital that developers can select vendors with the knowledge and confidence that their hardware and tools will support a standard: not only now but in the future. The fact is, the importance of standards in open source is just as great, if not more so, compared to proprietary architectures. The trace process needs to be efficient in terms of on-chip and input/output (I/O) requirements, and also needs to be designed for 21st century systems which are increasingly made up of many, many cores. In such systems every bit counts…and there are a lot of bits! To that end, we set up the RISC-V Processor Trace Task Group to define the trace standard and that meant we had to address three main areas:

- The interface between the RISC-V core and the trace encoder

- An efficient compressed branch trace algorithm to be implemented in an encoder

- A novel and highly efficient packet format which is output by the encoder

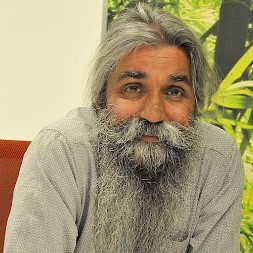

Gajinder “Gadge” Panesar is the Chief Technology Officer of UltraSoC and Chair of the RISC-V Processor Trace Task Group. As one of Europe’s leading SoC architects, Gadge’s experience includes senior architecture definition and design roles within both blue-chip and start-up environments. He holds more than 20 patents and is the author of more than 20 published works. Prior to joining UltraSoC, he served at NVIDIA (NASDAQ:NVDA). As Chief Architect at Picochip he created the architecture of the company’s market-defining small-cell SoCs, and continued in this capacity after the company’s acquisition by Mindspeed Inc (NASDAQ:MSPD). His previous experience includes roles at STMicroelectronics, INMOS, and Acorn Computers. He is a former Research Fellow at the UK’s Southampton University, and a former Visiting Fellow at the University of Amsterdam.[/vc_column_text][/vc_column][/vc_row]]]>

Gajinder “Gadge” Panesar is the Chief Technology Officer of UltraSoC and Chair of the RISC-V Processor Trace Task Group. As one of Europe’s leading SoC architects, Gadge’s experience includes senior architecture definition and design roles within both blue-chip and start-up environments. He holds more than 20 patents and is the author of more than 20 published works. Prior to joining UltraSoC, he served at NVIDIA (NASDAQ:NVDA). As Chief Architect at Picochip he created the architecture of the company’s market-defining small-cell SoCs, and continued in this capacity after the company’s acquisition by Mindspeed Inc (NASDAQ:MSPD). His previous experience includes roles at STMicroelectronics, INMOS, and Acorn Computers. He is a former Research Fellow at the UK’s Southampton University, and a former Visiting Fellow at the University of Amsterdam.[/vc_column_text][/vc_column][/vc_row]]]>