Chile is embarking on an exciting journey into the world of RISC-V. As the country takes its initial steps with RISC-V, there is growing enthusiasm and a wealth of opportunities to harness this technology for national development, education, and economic growth.

Emerging RISC-V Initiatives in Chile

At the forefront of Chile’s engagement with RISC-V is the Universidad Técnica Federico Santa María (UTFSM), where a series of pioneering projects are laying the groundwork for broader adoption:

Educational Integration

- Curriculum Development: The RISC-V ISA has been incorporated into the mandatory undergraduate Computer Architecture course for Electronics Engineering students at UTFSM. This initiative equips future engineers with knowledge of modern, open-standard architectures, preparing them for advancements in the tech industry.

- Collaborative Teaching Materials: Professors are collaborating with counterparts from other Chilean universities to develop shared teaching materials and educational tools in Spanish. This effort aims to make RISC-V more accessible to students nationwide, fostering a community of learners proficient in cutting-edge technology.

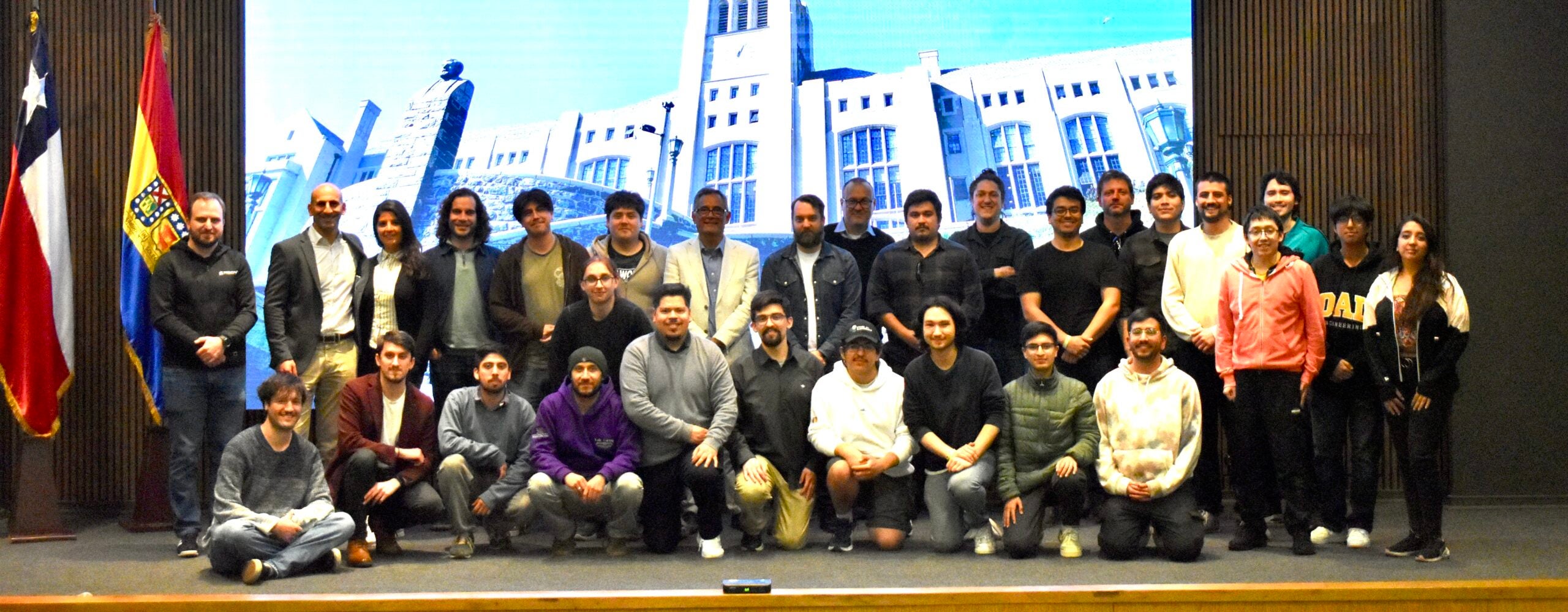

CANELOS 2024, Valparaíso – Chile.

Research and Development Projects

- First Chilean RISC-V Chip: A team at UTFSM successfully completed the country’s first RISC-V tapeout using the open-source SKY130 PDK and OpenLane design flow. The chip extends a single-cycle CPU to support the RV32I base instruction set and arrived for testing in August. This milestone demonstrates Chile’s growing capabilities in semiconductor design and sets the stage for future innovations.

- Synopsys Collaboration: Students received scholarships from Synopsys Chile to design a RISC-V chip using professional-grade electronic design automation (EDA) tools. By documenting the design process, they aim to create educational resources that will benefit future students and researchers.

- Asynchronous RISC-V Core Development: In partnership with local startup Timeless IC, students are developing an asynchronous version of a basic RISC-V core. This research explores new frontiers in processor design, potentially leading to processors with improved performance and energy efficiency.

- FPGA-Based Accelerators: Researchers at UTFSM are evaluating the use of RISC-V cores in field-programmable gate array (FPGA)-based accelerators for applications in automatic control and power electronics. This could enhance the capabilities of embedded systems across various industries, offering cost-effective and customizable solutions.

Key Academic Leaders

The progress in RISC-V initiatives at UTFSM is guided by dedicated professors passionate about technological innovation:

- Dr. Gonzalo Carvajal – Department of Electronics, specializing in Digital Systems and Computer Structures.

- Dr. Ioannis Vourkas – Department of Electronics, focusing on Digital Systems and Computer Structures.

- Dr. Christian Rojas – Department of Electronics, an expert in Power Electronics.

- Dr. Jorge Marín – Associated Researcher at AC3E, specializing in Power Electronics.

The Road Ahead

Chile’s foray into RISC-V marks a significant step toward embracing open-standard technologies that can drive national development. By focusing on current initiatives and recognizing the potential opportunities, Chile is well-positioned to become a leader in technological innovation within the region.

The commitment of educational institutions like UTFSM and the enthusiasm of students and researchers highlight a bright future for RISC-V in Chile. As the country continues to build on these initial steps, there is immense potential for RISC-V to transform industries, enhance education, and contribute to economic growth.

Embracing RISC-V is not just about adopting a new technology; it’s about fostering a culture of innovation, collaboration, and openness. Chile’s journey with RISC-V can serve as inspiration for other countries looking to harness the power of open-standard architectures to achieve technological sovereignty and prosperity.