SiFive FU740 PCIe Support Queued Ahead Of Linux 5.13 | Michael Larabel, phoronix

Arguably the most interesting RISC-V board announced to date is SiFive's HiFive Unmatched with the FU740 RISC-V SoC that features four U74-MC cores and one S7 embedded... Read more.

RISC-V Raspberry Pi Alternative Edges Closer to Release | Ian Evenden, Toms Hardware

D1 puts RISC-V into the hands of makers everywhere

A potential new Raspberry Pi competitor will soon be announced, according to a post on embedded systems blog CNX-Software.... Read more.

Espressif’s ESP32-C6 brings the next generation wireless connectivity | Open Cloudware

Espressif recently launched the ESP32-C6, which adds up to its long list of ESP32 series of SoCs. The ESP32-C6 is claimed to be the company’s first low-power and... Read more.

SiFive Tapes Out Their First 5nm RISC-V Processor Core | Michael Larabel

SiFive's OpenFive business unit announced today they have completed their first tape out of a RISC-V processor core using TSMC's 5nm process.

This 5nm RISC-V SoC... Read more.

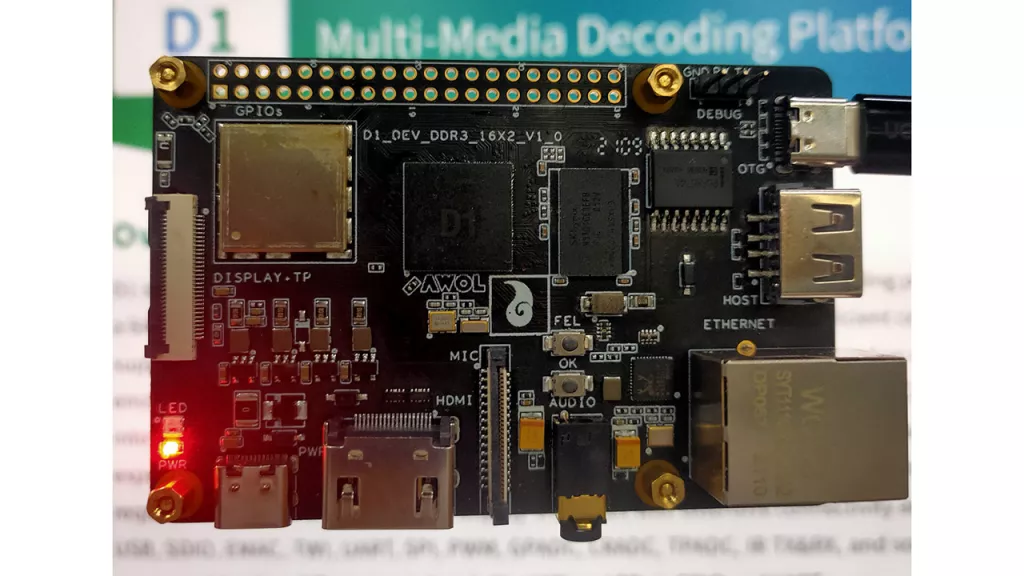

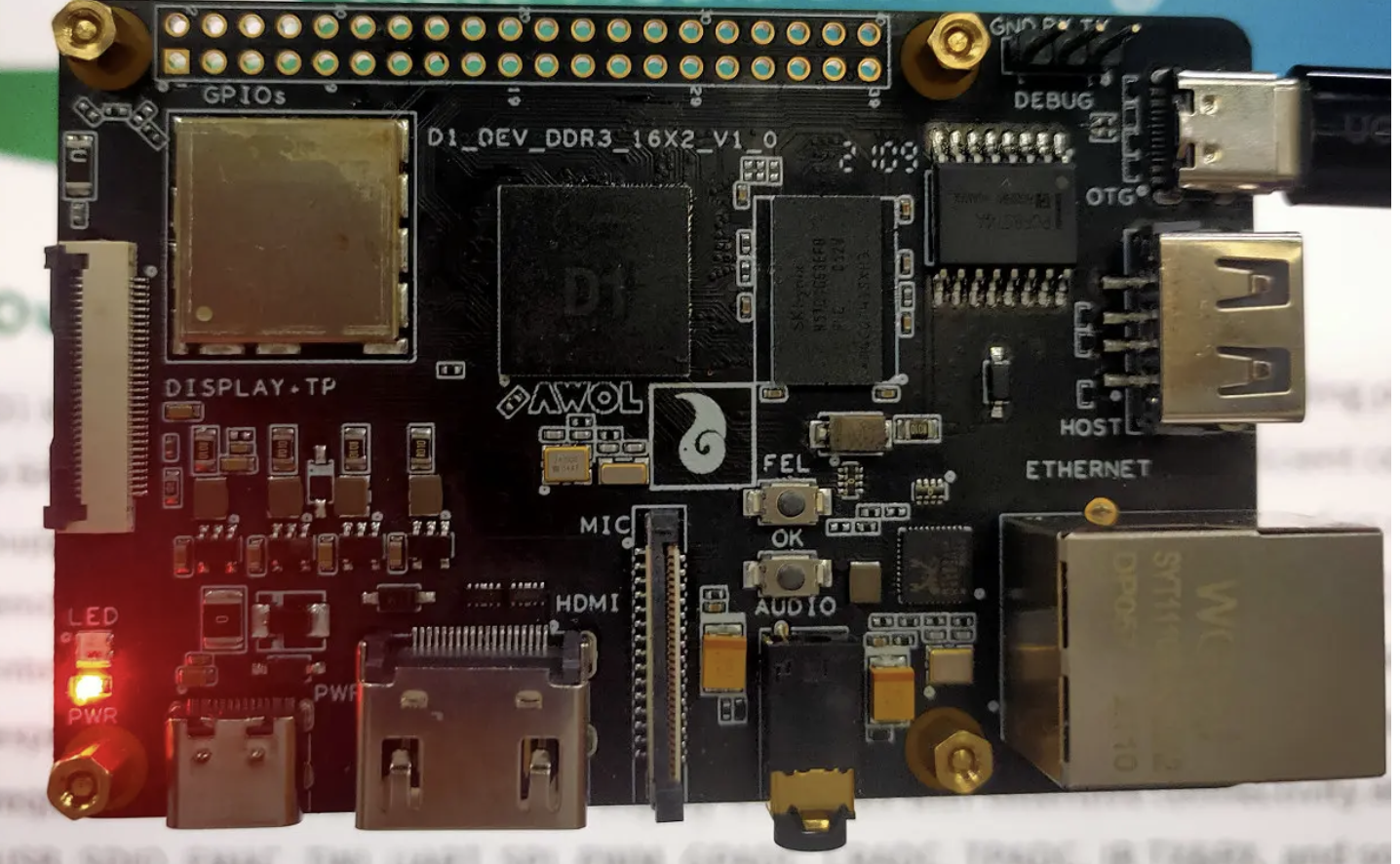

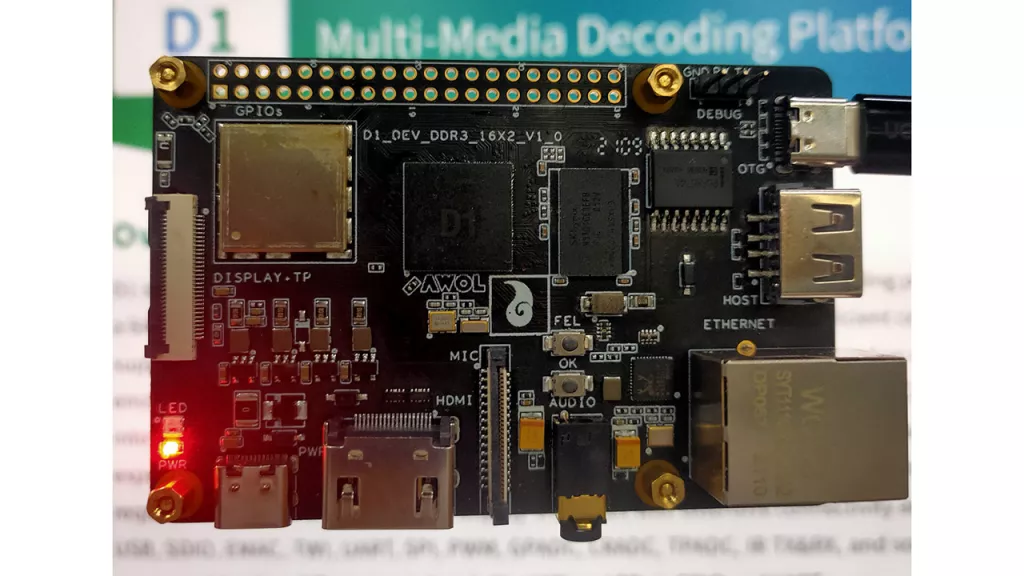

A first look at Allwinner D1 Linux RISC-V SBC and Processor | Jean-Luc Aufranc, CNX Soft

Last year, we reported that Allwinner was working on an Alibaba XuanTie C906 based RISC-V processor that would be found in low-cost Linux capable single board computers... Read more.

Homebrew RISC-V Computer Has Beauty and Brains | Tom Nardi, Hackaday

Building your own CPU is arguably the best way to truly wrap your head around how all those ones and zeros get flung around inside of a computer, but as you can... Read more.

Low-Cost Single-Board Computers with RISC-V Chips are Coming Soon | Brad Linder, liliputing

The first single-board computers powered by an Allwinner Xuantie-C906 processor could be set to ship soon. The chip isn’t exactly a speed demon, but it is expected... Read more.

Video: The Future of RISC-V in HPC – Vadim Malenboim, Sr Field Application Engineer, SiFive Core IP

RISC-V Architecture is widely adopted in the embedded and IoT market. The next phase of RISC-V Architecture evolution is the HPC segment. The SiFive portfolio includes... Read more.

SiFive Tapes Out First 5nm TSMC RISC-V Chip With 7.2 Gbps HBM3 | Anton Shilov, Tom’s Hardware

SiFive and OpenFive hit 5nm milestone.

SiFive on Tuesday said that that its OpenFive division has successfully taped out the company's first system-on-chip (SoC)... Read more.

From NIST to RISC-V: PQShield continues its leading role in international cryptography standardisation efforts for software and hardware | Dr Ali El Kaafarani

PQShield announces appointment of Ben Marshall, editor and main author of the RISC-V “K’ Cryptography Extension, to bolster its hardware division

PQShield,... Read more.