Espressif's ESP32-C3 Leaks as a Drop-In Pin-Compatible RISC-V Replacement for the Popular ESP8266 | Gareth Halfacree, hackster.io

After the introduction of an ultra-low-power RISC-V core in the ESP32-S2, Espressif is looking to launch its first RISC-V-only part. Read the full article. ]]>... Read more.

Webinar Download: Static Verification for RISC-V Cores and SoCs | Aldec

Description: The entire processor industry is currently going through a paradigm shift – new generations of domain-specific proprietary processor cores based... Read more.

Webinar Download: RISC-V Design and Verification with FPGA Hardware In The Loop | Aldec

Description: The RISC-V ISA has opened tremendous opportunities creating a breeze of fresh air in the ARM dominated design houses of embedded SoC projects. We didn’t... Read more.

An Automated Scalable RISC-V Cache Coherency Verification Project | Breker Verification Systems

Find out more about Breker’s RISC-V TrekApp: https://brekersystems.com/products/ri… Find out more about Breker’s Cache Coherency TrekApp: https://brekersystems.com/products/ca…[vc_row... Read more.

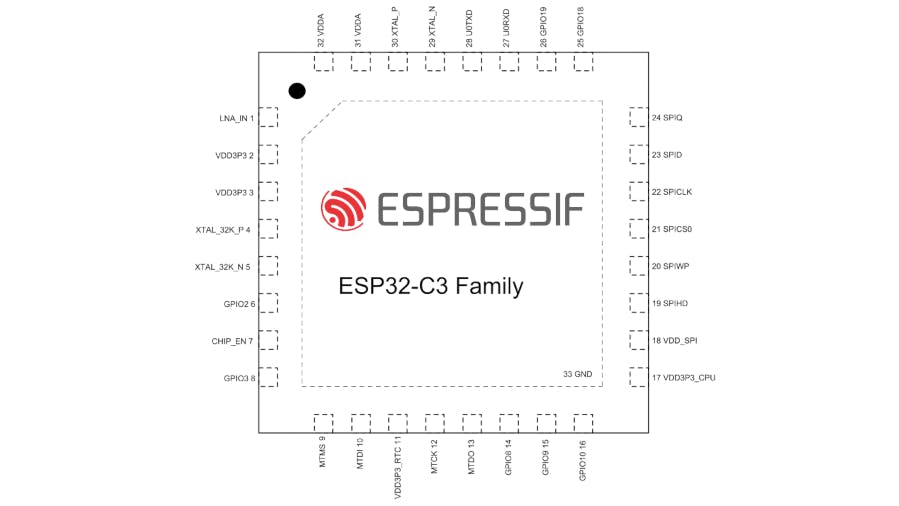

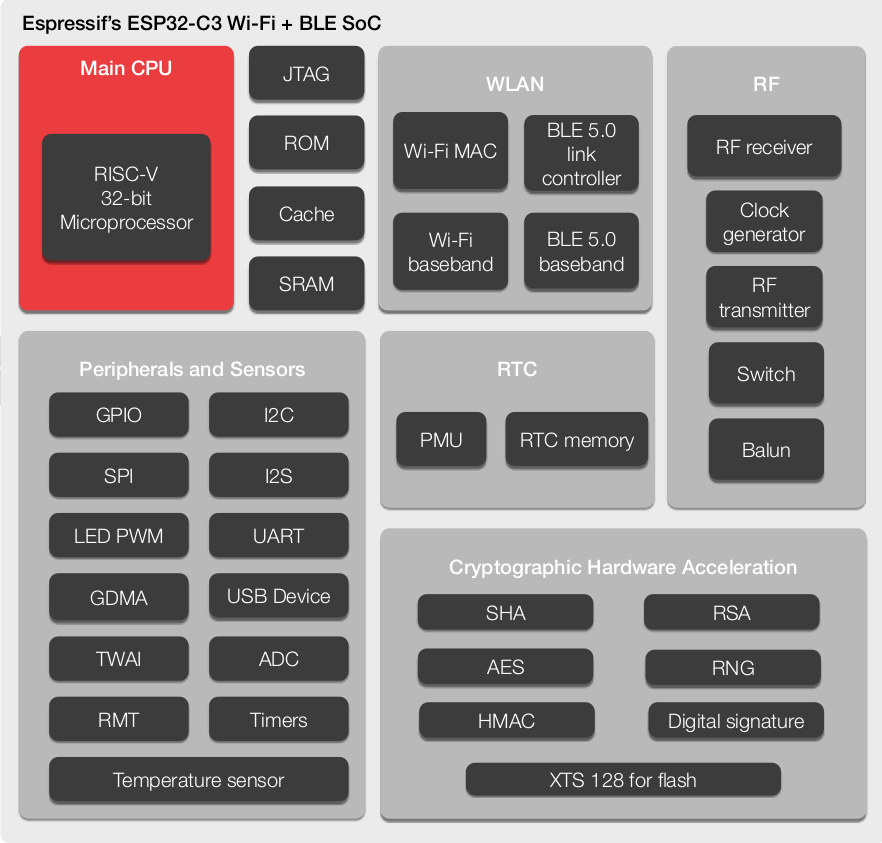

ESP32-C3 WiFi & BLE RISC-V processor is pin-to-pin compatible with ESP8266 | JEAN-LUC AUFRANC (CNXSOFT)

ESP32-S2-MINI modules last September, we also noted Espressif teased us with ESP32-S3 and ESP32-C3 with close to no details. ESP32-S3 is expected to be a multi-core... Read more.

Building coreboot for RISC-V and running it in Qemu | Wojciech Niewiadomski, 3MDEB

Read the full article.]]>... Read more.

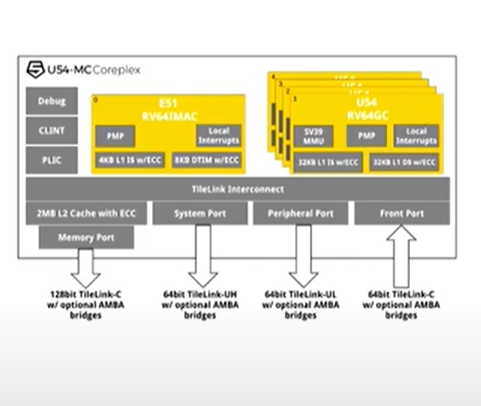

SiFive Strengthens Foothold in Storage Applications for Data-Centric AI Computing | James Prior, SiFive

FADU launched industry-leading SSD solutions powered by SiFive RISC-V Core IP. SiFive’s S51 RISC-V core IP enabled FADU Annapurna controller with 64-bit processing... Read more.