Today’s system-on-chip (SoC) designs integrate unprecedented numbers of diverse IP cores, from general-purpose CPUs to specialized hardware accelerators, including neural processing units (NPUs), tensor processors, and data processing units (DPUs). This heterogeneous approach enables designers to optimize performance, power efficiency, and cost. However, it also increases the complexity of on-chip communication, synchronization, and interoperability.

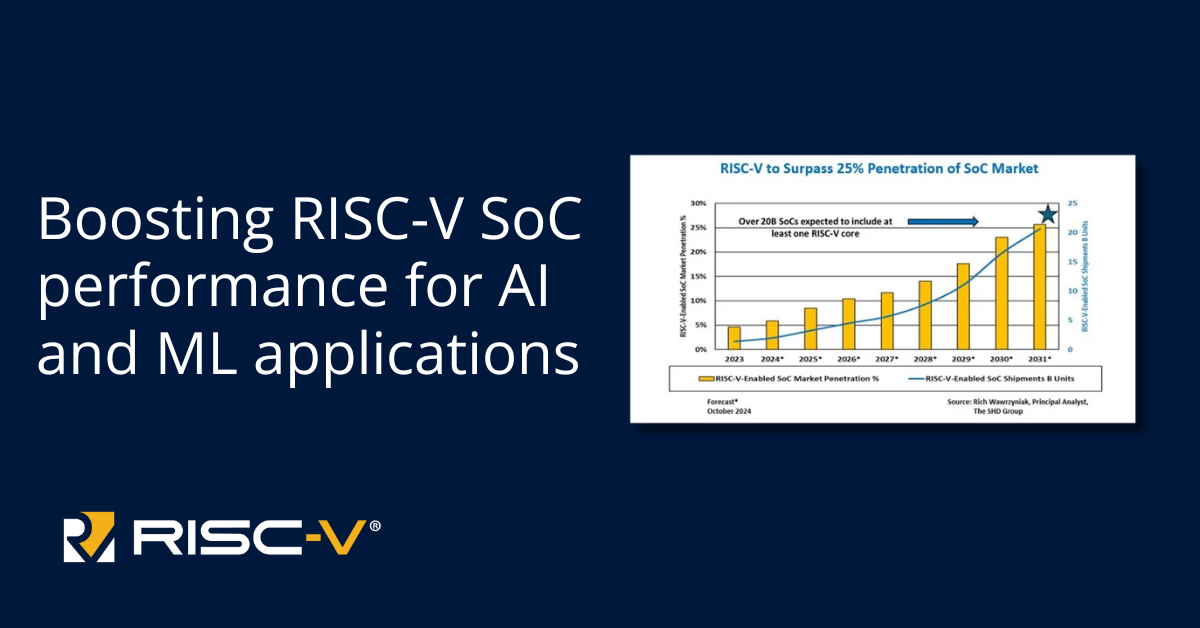

At around the same time, the open and configurable RISC-V instruction set architecture (ISA) is experiencing rapid adoption across diverse markets. This growth aligns with rising SoC complexity and the widespread integration of artificial intelligence (AI), as illustrated in figure below. Nearly half of global silicon projects now incorporate AI or machine learning (ML), spanning automotive, mobile, data center, and Internet of Things (IoT) applications. This rapid RISC-V evolution is placing increasing demands on the underlying hardware infrastructure.