Demonstrating PULSE Sensor using VEGA Microprocessor based on RISC-V ISA

Read More

RISC-V is a free and open instruction set architecture (ISA) enabling a new era of processor innovation through open standard collaboration. To help individuals get started with the RISC-V, the…

Read More

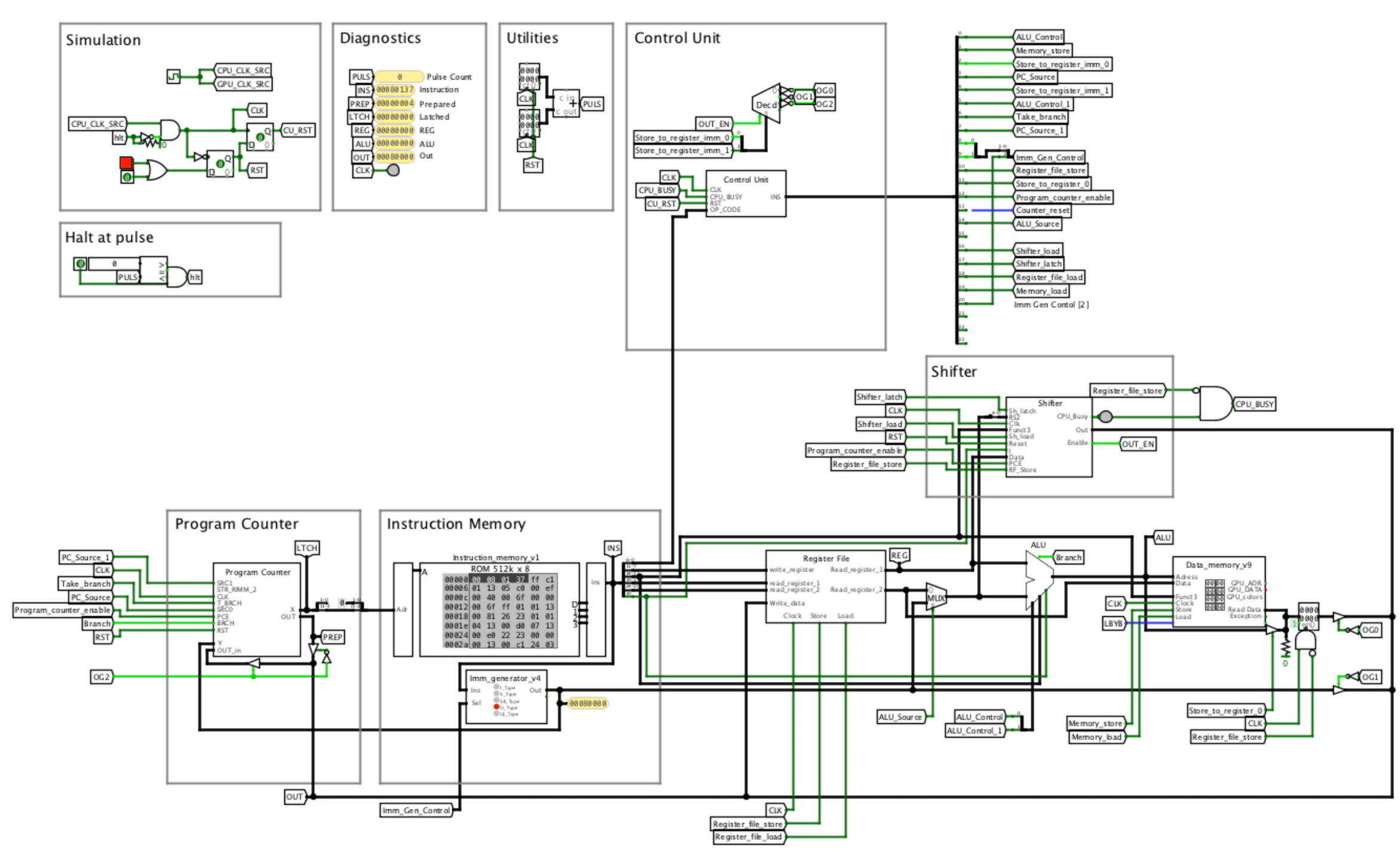

In this article I will describe how I designed and made a functional 32 bit RISC-V CPU at home. Specifications: "Max" clock speed: 500 kHz Program memory: 512 kB RAM…

Read More

Originally created to meet Antmicro’s internal need for a flexible system design and testing tool, Renode has been in use by numerous projects and organizations including internet giants like Google, Microsoft and…

Read More

Espressif launched ESP32-C3 at the end of 2020. It’s very well received and now it’s already in the mass production state. ESP32-C3 provides Wi-Fi and Bluetooth LE connectivity for applications…

Read More

Demonstrating 16X4 LCD Display using VEGA Microprocessor based on RISC-V ISA

Read More

ESP32-C3 is the first RISC-V wireless SoC from Espressif Systems, and at the time of the initial announcement promised to cost about the same as ESP8266 but adds support for…

Read More

Functional Test of Fabricated RISC-V Processor Cores to Demonstrate Hardware Security

Read More

RISC-V is a free and open instruction set architecture (ISA) enabling a new era of processor innovation through open standard collaboration. To help individuals get started with the RISC-V, the…

Read More

HSINCHU CITY, TAIWAN, April 23, 2021 (GLOBE NEWSWIRE) -- Andes Technology Corporation (TWSE: 6533), a leading supplier of high efficiency, low-power 32/64-bit RISC-V processor cores and Founding Premier member of…

Read More