Proposed RISC-V vector instructions crank up computing power on small devices | Agam Shah, The Register

Proposed RISC-V vector instructions crank up computing power on small devices | Agam Shah, The RegisterRISC-V looks set to be extended to bring more computing power to applications on smaller devices. The Zve collection of software instructions, right now under public…

Machine Learning: Esperanto coaxes 1092 RISC-V Processors to Dance on the Head of a Pin, er Chip | Amelia Dalton . Electronic Engineering Journal

Machine Learning: Esperanto coaxes 1092 RISC-V Processors to Dance on the Head of a Pin, er Chip | Amelia Dalton . Electronic Engineering JournalDave Ditzel has a legendary history with computing and microprocessors. He joined AT&T Bell Labs to work on C language development. While there, he developed…

OpenBSD 7.0 adds 64-bit RISC-V, improves Apple Arm silicon support | Jean-Luc Aufranc, CNX Software

OpenBSD 7.0 adds 64-bit RISC-V, improves Apple Arm silicon support | Jean-Luc Aufranc, CNX SoftwareOpenBSD 7.0, the 51st release of the UNIX-like operating system, was outed on October 14, 2021, with the introduction of 64-bit RISC-V support for HiFive…

HarmonyOS development board shows up for $11 | Jean-Luc Aufranc, CNX Software

HarmonyOS development board shows up for $11 | Jean-Luc Aufranc, CNX SoftwarePosted on October 18, 2021 by Jean-Luc Aufranc (CNXSoft) - 8 Comments on HarmonyOS development board shows up for $11 HarmonyOS development board shows up…

LILYGO’s New TTGO T-32C3 Is a Compact, Sub-$3 Espressif ESP32-C3 RISC-V Microcontroller Module | Gareth Halfacree, Hackster.io

LILYGO’s New TTGO T-32C3 Is a Compact, Sub-$3 Espressif ESP32-C3 RISC-V Microcontroller Module | Gareth Halfacree, Hackster.ioFeaturing castellated pin headers for surface-mount or partial breadboard compatibility, this low-cost module is a great entry to RISC-V. Embedded computing specialist LILYGO has launched…

The 5th AI Edge Contest (Implementation Contest 3) Vehicle Driving Image Recognition using RISC-V | Signate

The 5th AI Edge Contest (Implementation Contest 3) Vehicle Driving Image Recognition using RISC-V | SignateWith the progress of artificial intelligence (AI) technology, social implementation such as image recognition using AI technology, automatic driving, and natural language processing is rapidly…

You are students and like new challenges. You are interested in electronics and computer architectures and want to participate in the design of a renowned…

In modern digital camera systems, the captured image undergoes a complex process involving various image signal processing (ISP) techniques to reproduce the observed scene as…

Enthusiasts dash for RISC-V computer with GPU | Agam Shah, The Register

Enthusiasts dash for RISC-V computer with GPU | Agam Shah, The RegisterIt seems computers without an Arm or x86 chip are in serious demand in the RISC-V community. A Raspberry Pi-like small-board computer with an RISC-V…

“Una versión de Windows para RISC-V es posible”: hablamos con Roger Espasa, CEO de Semidynamics | Javier Pastor, Xataka

“Una versión de Windows para RISC-V es posible”: hablamos con Roger Espasa, CEO de Semidynamics | Javier Pastor, XatakaNo ocurre todos los días que Europa lance un chip propio. Lo hicieron estos días con el EPAC1.0, un SoC que destacaba por utilizar la…

Green Hills covers RISC-V with Integrity | Steve Bush, Electronics Weekly

Green Hills covers RISC-V with Integrity | Steve Bush, Electronics WeeklyGreen Hills Software has announced a version of its safety and security-enhanced Integrity real-time operating system for RISC-V. The RTOS is integrated with hardware boards…

Vortex: Extending the RISC-V ISA for GPGPU and 3D-Graphics Research | Blaise Tine, Fares Elsabbagh, Krishna Yalamarthy, and Hyesoon Kim, Georgia Institute of Technology

Vortex: Extending the RISC-V ISA for GPGPU and 3D-Graphics Research | Blaise Tine, Fares Elsabbagh, Krishna Yalamarthy, and Hyesoon Kim, Georgia Institute of TechnologyThe importance of open-source hardware and software has been increasing. However, despite GPUs being one of the more popular accelerators across various applications, there is…

Espressif launched ESP32-C3 at the end of 2020. It’s very well received and now it’s already in the mass production state. ESP32-C3 provides Wi-Fi and…

Demonstrating 16X4 LCD Display using VEGA Microprocessor based on RISC-V ISA

AI-Thinker introduces 5 ESP32-C3 modules pin compatible with ESP8266 & ESP32 modules | Jean-Luc Aufranc, CNX Soft

AI-Thinker introduces 5 ESP32-C3 modules pin compatible with ESP8266 & ESP32 modules | Jean-Luc Aufranc, CNX SoftESP32-C3 is the first RISC-V wireless SoC from Espressif Systems, and at the time of the initial announcement promised to cost about the same as…

Functional Test of Fabricated RISC-V Processor Cores to Demonstrate Hardware Security

New Online Courses For RISC-V | The Linux Foundation

New Online Courses For RISC-V | The Linux FoundationRISC-V is a free and open instruction set architecture (ISA) enabling a new era of processor innovation through open standard collaboration. To help individuals get…

Andes Announces the New Upgrade of AndeSight™ IDE v5.0: a comprehensive software solution to accelerate RISC-V AI and IoT developments | Globe Newswire

Andes Announces the New Upgrade of AndeSight™ IDE v5.0: a comprehensive software solution to accelerate RISC-V AI and IoT developments | Globe NewswireHSINCHU CITY, TAIWAN, April 23, 2021 (GLOBE NEWSWIRE) -- Andes Technology Corporation (TWSE: 6533), a leading supplier of high efficiency, low-power 32/64-bit RISC-V processor cores…

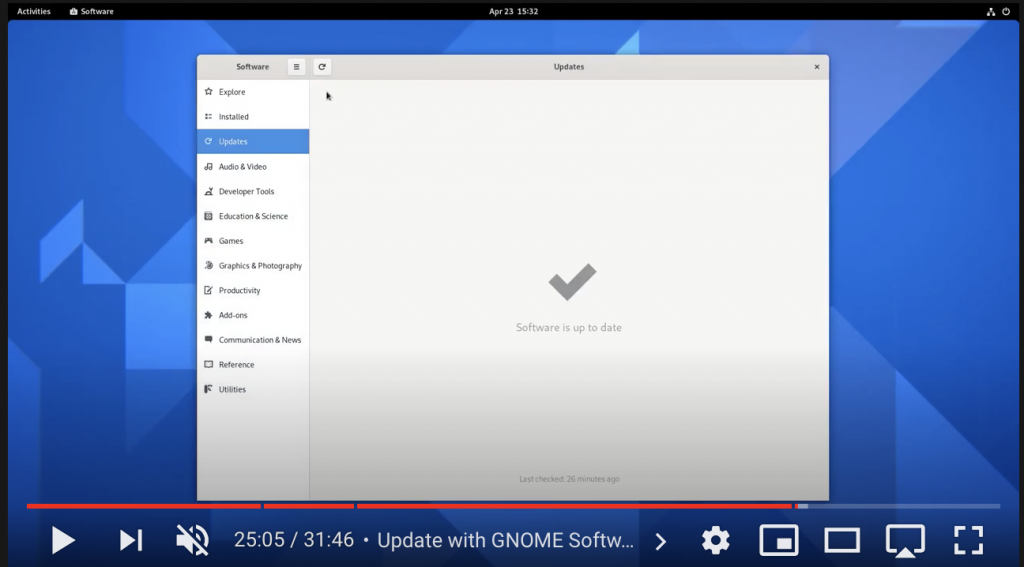

Video: GNOME OS on RISC-V |

Video: GNOME OS on RISC-V |This video shows installation and update of GNOME OS onto a RISC-V virtual machine.

Tenstorrent Selects SiFive Intelligence X280 for Next-Generation AI Processors

Tenstorrent Selects SiFive Intelligence X280 for Next-Generation AI ProcessorsSiFive Intelligence IP integral component of future Tenstorrent AI architectures SAN MATEO, Calif., April 22, 2021 – SiFive, Inc., the industry leader in RISC-V processors and silicon…

Video: De-RISC project

Video: De-RISC projectThe De-RISC (Dependable Real-time Infrastructure for Safety-critical Computer) project addresses computer systems within the space and aviation domains. De-RISC – Dependable Real-time Infrastructure for Safety-critical…

How a National Effort Could Help End the Chip Shortage | Sascha Brodsky, Lifewire

How a National Effort Could Help End the Chip Shortage | Sascha Brodsky, LifewireUS factories could meet demand, eventually Key Takeaways Experts are calling for a national investment in chip manufacturing to ensure that users can get everything…

Open-source architecture is gaining some traction in more complex designs as ecosystem matures. RISC-V vendors are beginning to aim much higher in the compute hierarchy,…

RISC-V vendors are beginning to aim much higher in the compute hierarchy, targeting data centers and supercomputers rather than just simple embedded applications on the…