New release of SweRVolf RISC-V SoC project aims for lower barrier to entry | Gareth Halfacree, The Register

New release of SweRVolf RISC-V SoC project aims for lower barrier to entry | Gareth Halfacree, The RegisterThe SweRVolf project, a fully open system-on-chip designed as a reference platform for Western Digital's RISC-V SweRV cores, has announced a major new release promising…

Lup Yuen Lee is a hands-on IoT advisor and educator who is passionate about helping everyone create IoT products that make a difference to the…

Read the full newsletter, including RISC-V highlights.

Synopsys Accelerates Most Stringent Functional Safety Certification of NSITEXE RISC-V Parallel Processor IP | Design and Reuse

Synopsys Accelerates Most Stringent Functional Safety Certification of NSITEXE RISC-V Parallel Processor IP | Design and ReuseFirst ISO 26262 ASIL D Certified RISC-V Processor with Vector Extension Tapped into Speed and Capacity of Synopsys Z01X Fault Simulation Solution Accelerating its leadership…

Linked but not the same - take a look at Luca Benini's recent presentation from Visions of ECS beyond 2030 that among other things discusses the…

As global economic uncertainty and trade tensions between the United States, China and Taiwan accelerate the movement to localize the supply chain to produce and…

Forget Microservices: A NIC-CPU Co-Design For The Nanoservices Era | Timothy Prickett Morgan, The Next Platform

Forget Microservices: A NIC-CPU Co-Design For The Nanoservices Era | Timothy Prickett Morgan, The Next PlatformThe remote procedure call, or RPC, might be the single most important invention in the history of modern computing. The ability to reach out from…

Andes Technology Corp. Brings Its Broad Family of RISC-V CPU IP to the Silicon Catalyst Semiconductor Incubator | Chip Estimate

Andes Technology Corp. Brings Its Broad Family of RISC-V CPU IP to the Silicon Catalyst Semiconductor Incubator | Chip EstimateAndes Technology Corporation (TWSE: 6533), a leading supplier of high efficiency, low-power 32/64-bit RISC-V processor cores and Founding Premier member of RISC-V International, today announced…

Getting started with Bluetrum AB32VG1 RISC-V Bluetooth audio board using RT-Thread | Jean-Luc Aufranc, CNX Software

Getting started with Bluetrum AB32VG1 RISC-V Bluetooth audio board using RT-Thread | Jean-Luc Aufranc, CNX SoftwareBluetrum AB32VG1 is a development board based on AB5301A RISC-V microcontroller designed for Bluetooth audio applications as well as general-purpose projects that works with RT-Thread…

The CFU-Playground allows anyone to build FPGA based accelerators for ML inferencing. With a heavy reliance on the Python based tools LiteX and nMigen, it…

Why It’s the Perfect Time to Join Codasip and be Part of the RISC-V Revolution | Rupert Baines, CMO Codasip

Why It’s the Perfect Time to Join Codasip and be Part of the RISC-V Revolution | Rupert Baines, CMO CodasipEighteen months ago, I said: “The rise of RISC-V offers us a tremendous platform for innovation and collaboration: it has the potential to change the business model…

RISC-V to Shake up $8.6-Billion Semiconductor IP Market | William Li, Counterpoint Research

RISC-V to Shake up $8.6-Billion Semiconductor IP Market | William Li, Counterpoint ResearchIP design around the chipset architecture, security and cutting-edge performance improvements has been the key to the semiconductor supply chain. Intel has been dominating the…

Video: MAX30102 Pulse Oximeter and Heart Rate Sensor Demo using VEGA Processor [ RISC-V ISA]

Video: MAX30102 Pulse Oximeter and Heart Rate Sensor Demo using VEGA Processor [ RISC-V ISA]Demonstrating MAX30102 Pulse Oximeter and Heart Rate Sensor using VEGA Microprocessor based on RISC-V ISA Source code : https://gitlab.com/cdac-vega/

RISC-V XIP Support Queued Ahead Of Linux 5.13 To “eXecute In Place” | Michael Larabel

RISC-V XIP Support Queued Ahead Of Linux 5.13 To “eXecute In Place” | Michael LarabelIt looks like the Linux 5.13 kernel will be supporting an interesting RISC-V feature this spring. Queued up now in RISC-V's "for-next" branch as of this week…

Valtrix and Codasip Cooperate on Verification of RISC-V Systems

Valtrix and Codasip Cooperate on Verification of RISC-V SystemsBangalore, India and Munich, Germany – March 23rd, 2021 – Valtrix Systems, the provider of design verification products for building functionally correct CPU and system-on-chip…

In $20bn push, Intel hopes to make US chip-making great again | Aljazeera

In $20bn push, Intel hopes to make US chip-making great again | AljazeeraIntel plans to build two factories in Arizona in challenge to Taiwanese, South Korean advanced chip-making giants. Read the full article.

Verification In The Open Source Era | Brian Bailey, Semiconductor Engineering

Verification In The Open Source Era | Brian Bailey, Semiconductor EngineeringWhat does open-source verification mean in the context of a RISC-V processor core? Does it provide free tools, free testbenches, or the freedom to innovate?…

We are surrounded by electronic devices that make the modern world work. Almost all of these devices and the systems they run are “Embedded Systems”,…

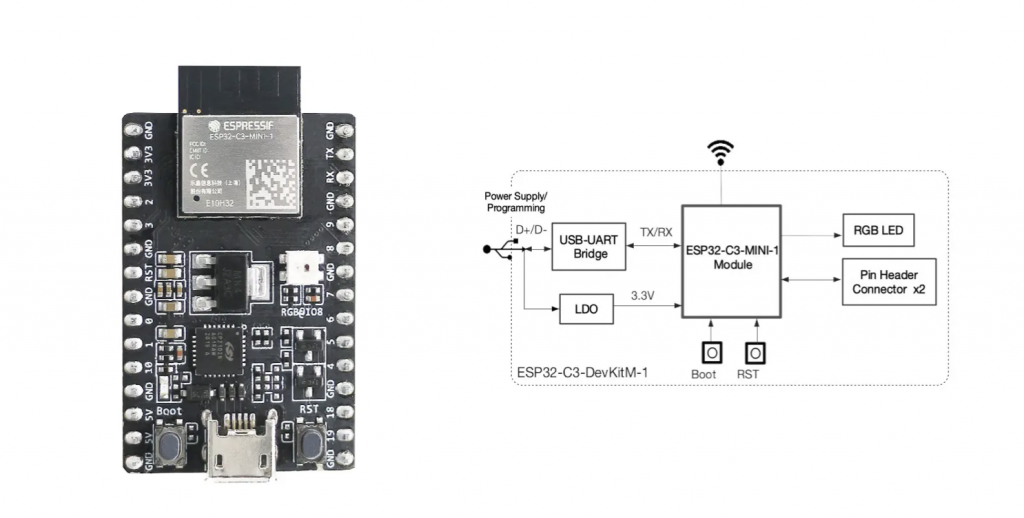

ESP32-C3-DevKitM-1 RISC-V WiFI & BLE board to launch for $8, modules for $1.8+ | JEAN-LUC AUFRANC (CNXSOFT)

ESP32-C3-DevKitM-1 RISC-V WiFI & BLE board to launch for $8, modules for $1.8+ | JEAN-LUC AUFRANC (CNXSOFT)ESP32-C3 may be one of the most expected RISC-V processors in the IoT world, as it’s eventually expected to sell for the same price as…

SiFive collaborates with new Intel Foundry Services to enable innovative new RISC-V computing platforms | Sifive Blog – Patrick Little, President & CEO, SiFive

SiFive collaborates with new Intel Foundry Services to enable innovative new RISC-V computing platforms | Sifive Blog – Patrick Little, President & CEO, SiFiveEnabling more choice for Next-Generation Heterogeneous Compute Platforms I am excited to see Intel's new Foundry services business (IFS) in the U.S. and Europe increase…

IAM949- CEO Expands and Engages Company’s Stakeholders | Podcast Interview with Calista Redmond

IAM949- CEO Expands and Engages Company’s Stakeholders | Podcast Interview with Calista RedmondCalista Redmond is the CEO of RISC-V International with a mission to expand and engage RISC-V stakeholders, compel industry adoption, and increase visibility and opportunity…

AndeSysC™ – A Flexible RISC-V Processor Model for SoC Virtual Prototyping | Andes Technology

AndeSysC™ – A Flexible RISC-V Processor Model for SoC Virtual Prototyping | Andes TechnologyAndeSysC™ is Andes virtual platform solution based on SystemC to enrich the RISC-V ecosystem. It provides extendable, flexible and near-cycle accurate models of AndesCore™ V5…

Initial research project awarded to CMC Microsystems, ETH Zürich, and Polytechnique Montréal will be presented on March 18 via OpenHW TV webinar. Register at https://bit.ly/3dMIay3…

SiFive collaborates with new Intel Foundry Services to enable innovative new RISC-V computing platforms | Patrick Little, SiFive

SiFive collaborates with new Intel Foundry Services to enable innovative new RISC-V computing platforms | Patrick Little, SiFiveEnabling more choice for Next-Generation Heterogeneous Compute Platforms I am excited to see Intel's new Foundry services business (IFS) in the U.S. and Europe increase…