Is RISC-V the future? This is a question that we often get asked, and let’s assume that we mean ‘is the RISC-V going to be…

Leading the RISC-V uprising drives SiFive, home of the inventors of RISC-V, to continue to push forward with developing our product families and technologies. Earlier…

Design flow of the DRAC project |

Design flow of the DRAC project |DRAC is a research project with the aim to produce RISC-V processors and different accelerators trying to achieve the maximum possible performance while minimizing power…

Russia to Build 8-Core RISC-V CPUs for Laptops, Government Systems | Joel Hruska, Extreme Tech

Russia to Build 8-Core RISC-V CPUs for Laptops, Government Systems | Joel Hruska, Extreme TechRISC-V has attracted a great deal of interest across the computing industry for its open-source instruction set architecture and rapidly evolving ecosystem. There are reports…

Together with industrial partners, the University of California, Berkeley has developed the „Reduced Instruction Set Computer V“ (RISC-V) using an open instruction set architecture (ISA).…

Computer scientist showcases world’s first RISC-V-based Linux PC coupled with an AMD RX 6700 XT GPU | Bogdan Solca, Notebook Check

Computer scientist showcases world’s first RISC-V-based Linux PC coupled with an AMD RX 6700 XT GPU | Bogdan Solca, Notebook CheckRené Rebe managed to patch the Linux kernel to support the RISC-V processor along with the AMD RX 6700 XT card in around 10 hours.…

Since last Friday, five openSUSE Tumbleweed snapshots have been released. GNOME 40, btrfs, Mesa, Wireshark and several other package updates landed this week in the…

World’s First Desktop PC RISC-V Board Meets AMD Radeon RX 6700 XT | Anton Shilov, Tom’s Hardware

World’s First Desktop PC RISC-V Board Meets AMD Radeon RX 6700 XT | Anton Shilov, Tom’s HardwareWhen SiFive introduced its HiFive Unmatchd RISC-V desktop motherboard for developers last year, it was clear from the start that sooner or later an enthusiast would attempt to…

Interview With Dirk Koch and Nguyen Dao | Matt Venn, Zero To ASIC

Interview With Dirk Koch and Nguyen Dao | Matt Venn, Zero To ASICRead the full article and watch the interview. "One of the popular types of entries to MPW1 & 2 have been FPGAs. I have previously…

What is Zephyr RTOS? Why would I chose Zephyr over Linux? How is it open source? What is the Zephyr Project and how does it…

Video: Pineapple One: An Open-Source Discrete 32-Bit RISC-V CPU

Video: Pineapple One: An Open-Source Discrete 32-Bit RISC-V CPUThis talk will be about a 32-bit homemade RISC-V CPU, made only out of discrete logic components and memories. There are no FPGAs nor any…

CAES Receives Contract from Vinnova to Advance High Performance RISC-V Space Computing

CAES Receives Contract from Vinnova to Advance High Performance RISC-V Space ComputingCAES, a leader in advanced mission-critical electronics for aerospace and defense, announced today that it has been awarded a contract from Vinnova, a Swedish government agency…

The Future Is Now: Mark Himelstein of RISC-V On How Their Technological Innovation Will Shake Up The Tech Scene | Fotis Georgiadis, Authority Magazine

The Future Is Now: Mark Himelstein of RISC-V On How Their Technological Innovation Will Shake Up The Tech Scene | Fotis Georgiadis, Authority MagazineSome of the greatest “rocket science” in RISC-V is the simplicity, elegance, and flexibility of it. While some of the individual pieces are not “rocket…

Formal Bytes, Episode 39: Abstraction in 7 minutes! | Axiomise Formal Verification Channel

Formal Bytes, Episode 39: Abstraction in 7 minutes! | Axiomise Formal Verification ChannelWe demystify abstraction in today's podcast. Abstraction is the cornerstone of modern-day scalable formal verification. Classic papers in formal literature talk about abstraction as a…

SiFive Helping To Teach Kids Programming With RISC-V HiFive Inventor Coding Kit | Michael Larabel, Phoronix

SiFive Helping To Teach Kids Programming With RISC-V HiFive Inventor Coding Kit | Michael Larabel, PhoronixSiFive in cooperation with Tynker and BBC Learning have launched a Doctor Who themed HiFive Inventor Coding Kit. This Initial HiFive Inventor Coding Kit is…

Open Hardware: Open Source conquering processors (French) | David Feugey, Silicon.fr

Open Hardware: Open Source conquering processors (French) | David Feugey, Silicon.frAu début des années 2000, une communauté d’ingénieurs veut allier électronique et Open Source. Leur idée : proposer des plans de cartes mères, de composants…

Very Efficient Deep Learning in IoT project with RISC-V and Renode | Antmicro

Very Efficient Deep Learning in IoT project with RISC-V and Renode | AntmicroWe are happy to announce our involvement in ‘Very Efficient Deep Learning in IoT’ (VEDLIoT) - a project funded by the European Commission and coordinated…

What Is RISC V: Should You Even Care | Brodie Robertson

What Is RISC V: Should You Even Care | Brodie RobertsonRISC V gets thrown around a lot but what is it and how does it differ from what we're already using on our desktop and…

HSINCHU, TAIWAN – January 14, 2021 – Andes Technology, a global leader in 32/64-bit RISC-V CPU core solutions, and Rafael Microelectronics, a leading provider for RF…

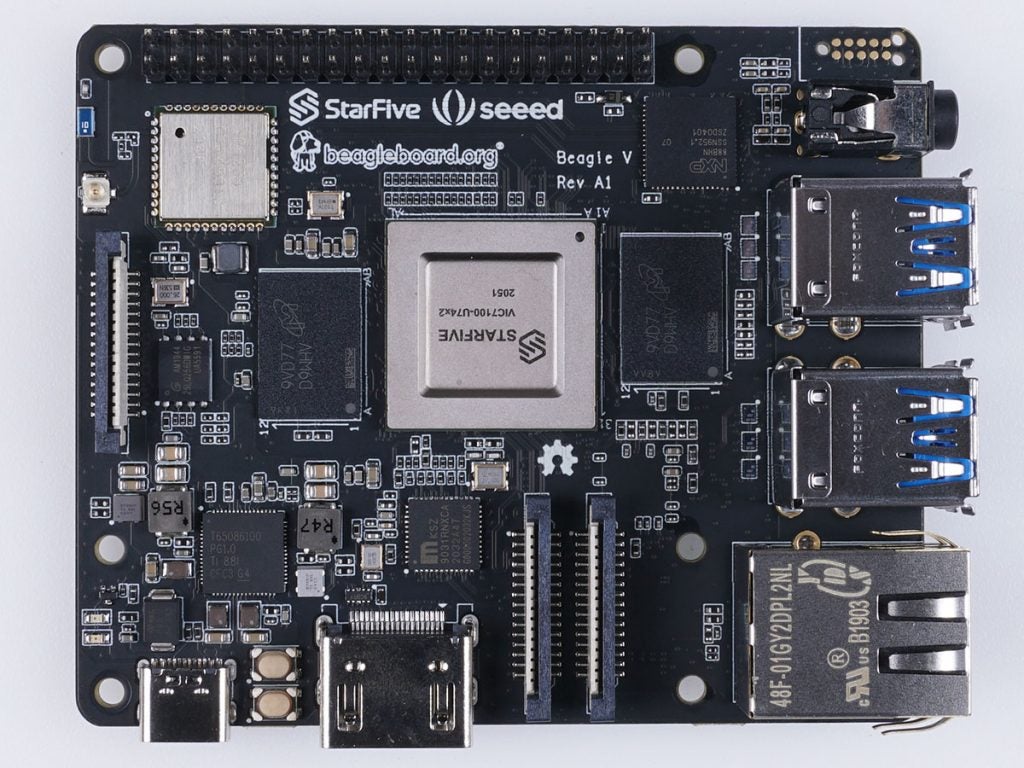

Move over, ARM: BeagleV is a $150 RISC-V computer designed to run Linux | Jim Salter, Ars Technica

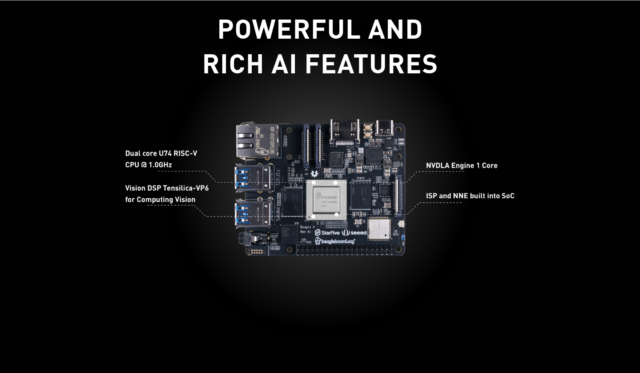

Move over, ARM: BeagleV is a $150 RISC-V computer designed to run Linux | Jim Salter, Ars TechnicaSeeed Studios—the makers of the Odyssey mini-PC we reviewed back in August—have teamed up with well-known SBC vendor BeagleBoard to produce an affordable RISC-V system designed to run Linux. The new…

What’s the RISC-V movement all about? What are the major misconceptions about RISC-V? Has it moved from initial experimentation to practical implementation? At the all-digital CES…

BeagleBoard.org® and Seeed introduces the first affordable RISC-V board designed to run Linux

BeagleBoard.org® and Seeed introduces the first affordable RISC-V board designed to run Linux January 13th, 2021, Shenzhen, China and Rochester MI, USA: Seeed and BeagleBoard.org® have announced an official collaboration with the leading RISC-V solutions provider, StarFive, to create the latest member of the BeagleBoard.org® series, BeagleV™ (pronounced Beagle five.) BeagleV™ is…