The Amp Hour Podcast welcomes back Antmicro's Michael Gielda who was on episode 519 talking about simulating embedded hardware using Renode He returned to talk…

Almost 700 people registered for the first-ever Zephyr Developer Summit, which took place virtually on June 8-10, to learn more about the RTOS. We had…

Watch a video tutorial showing the steps involved in creating a 32-bit RISC-V CPU. See the full video here.

Watch Filip Szkandera talk about a homemade 32-bit RISC-V CPU. It runs at 500 kHz, has 512 kB RAM & program memory. VGA output is…

Chinese chip designers hope to topple Arm’s Cortex-A76 with XiangShan RISC-V design | Gareth Halfacree, The Register

Chinese chip designers hope to topple Arm’s Cortex-A76 with XiangShan RISC-V design | Gareth Halfacree, The RegisterThe Institute of Computing Technology at the Chinese Academy of Sciences (ICT CAS) has showcased progress on a fully open-source processor, designed around the RISC-V…

GreenWaves releases Profiler – A visualization tool for profiling and debugging GAP applications

GreenWaves releases Profiler – A visualization tool for profiling and debugging GAP applicationsProfiler is a part of our GAP SDK and used with GVSOC, our Full System SoC Simulator. Profiler gives you a visual view of what…

XiangShan open-source 64-bit RISC-V processor to rival Arm Cortex-A76 | Jean-Luc Aufranc, CNX Software

XiangShan open-source 64-bit RISC-V processor to rival Arm Cortex-A76 | Jean-Luc Aufranc, CNX SoftwareSiFive Performance P550 was supposed to be the most powerful RISC-V core to date, capable of outperforming Arm’s Cortex-A75 core in raw performance, but especially in…

Open source software is omnipresent in the server and cloud world, with open source operating systems, container runtimes, as well as frameworks for device management,…

Video: Exception handling in a RISC-V core – Exercise #7 | Learn RISC-V

Video: Exception handling in a RISC-V core – Exercise #7 | Learn RISC-VThis video demonstrates load access fault exception generation and handling. It discusses the basic registers associated and configuring those. Watch the full video tutorial here. …

Announcing the Research Triangle RISC-V Community Group | Daniel Mangum

Announcing the Research Triangle RISC-V Community Group | Daniel MangumI am excited to announce the launch of the Research Triangle RISC-V Community Group! As evidenced by my recent posts and conference talks, I have been spending more and…

Week In Review: Design, Low Power | Jesse Allen, Semiconductor Engineering

Week In Review: Design, Low Power | Jesse Allen, Semiconductor EngineeringTools Imperas and Valtrix inked a multi-year distribution and support agreement that makes Imperas simulation technology and RISC-V reference models available pre-integrated within Valtrix STING for RISC-V processor verification.…

Andes Technology Announces Over 2 Billion Shipments Of Andes-Embedded SoCs In 2020

Andes Technology Announces Over 2 Billion Shipments Of Andes-Embedded SoCs In 2020Andes Technology (TWSE: 6533), a leading supplier of high efficiency, low-power 32/64-bit RISC-V processor cores, announced a remarkable record of 2 billion annual SoC shipments…

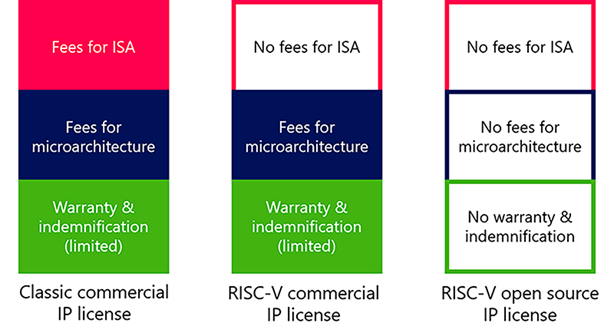

Open Source vs. Commercial RISC-V Licensing Models | Roddy Urquhart, Semiconductor Engineering

Open Source vs. Commercial RISC-V Licensing Models | Roddy Urquhart, Semiconductor Engineeringopen standard like C, Verilog, or HTTP is defined by a document that is maintained by an independent organization. Thus, C is maintained by ISO, Verilog by…

SoC project effort in terms of cost and time for a mature, mainstream processor IP core. But the processor IP business model is based on one-size-fits-all, which allows…

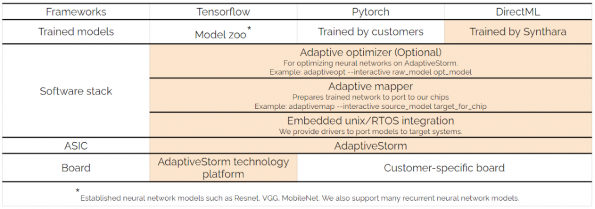

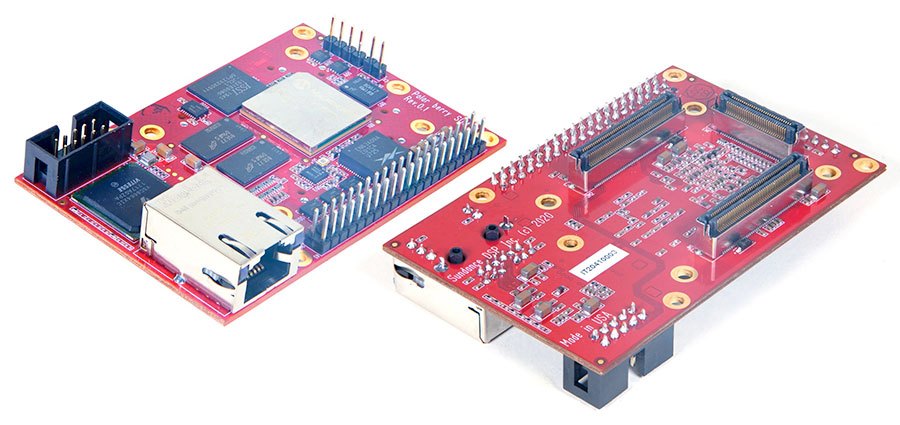

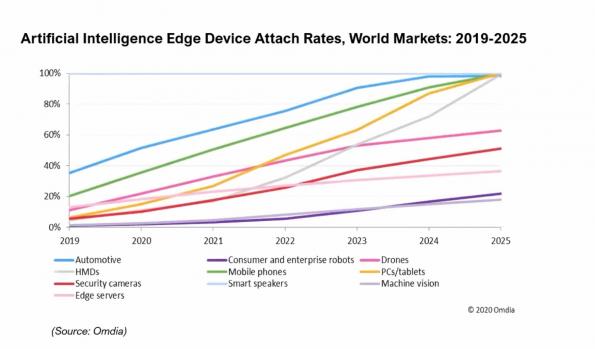

The year edge AI took off | Nick Flaherty, EE News Europe

The year edge AI took off | Nick Flaherty, EE News EuropeTHE AI CHIPS RACE IS ON – WHAT ROLE WILL IP PLAY? GRAI MATTER, PARIS RESEARCH GIVES RISE TO AI PROCESSOR FOR THE EDGE New…

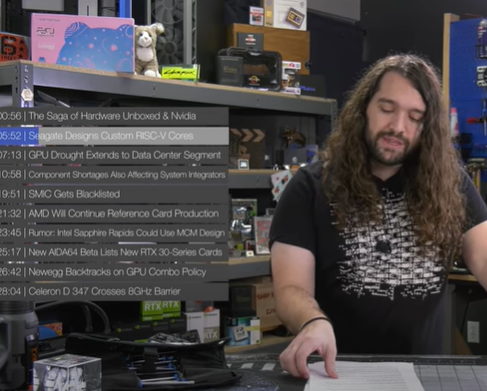

HW News – NVIDIA & Reviewers, RISC-V Core Designs, 8GHz Intel CPU OC, & CPU Shortages | Gamers Nexus

HW News – NVIDIA & Reviewers, RISC-V Core Designs, 8GHz Intel CPU OC, & CPU Shortages | Gamers NexusHardware news this week talks about NVIDIA's treatment of Hardware Unboxed and other reviewers, the GPU and component shortages, RISC-V emergence for CPUs, and more.…

DESK OF LADYADA – Brainwave Sunday + HiFive RISC-V Inventor Kit | Adafruit Industries

DESK OF LADYADA – Brainwave Sunday + HiFive RISC-V Inventor Kit | Adafruit IndustriesIt's a mega-mailbag day today, as we investigate two new dev kits we got this week: one is the Next Mind EEG/brain-sensor development platform with…

OpenRISC + RISC-V Improvements Come for Linux 5.11 | Michael Larabel, Phoronix

OpenRISC + RISC-V Improvements Come for Linux 5.11 | Michael Larabel, PhoronixLiteX is a Migen/MiSoC CPU/SoC builder for deployments on FPGAs. LiteX already supports soft-core implementations of PicoRV32, VexRISCV, and others. Read the full article]]>

general-purpose microcontrollers, AIoT processors, as well as WiFi and Bluetooth IoT SoC’s such as ESP32-C3 and BL602. Allwinner is also prepping a RISC-V application processor, and we’ve covered plenty of…

Cobham Gaisler élargit sa collaboration avec l’éditeur espagnol fentISS afin de promouvoir en commun le cœur de processeur Leon5 et le cœur compatible RISC-V Noel-V ainsi que l’hyperviseur…