Pine64 introduces Quartz64 single-board PC with RK3566 processor, teases upcoming RISC-V board | Brad Linder, Liliputing

Pine64 introduces Quartz64 single-board PC with RK3566 processor, teases upcoming RISC-V board | Brad Linder, LiliputingOne of the next single-board computers from Pine64 is a 5.2″ x 3.1″ mini PC powered by a 1.8 GHz Rockchip RK3566 ARM Cortex-A55 processor…

RISC-V: How much is open source? Featuring the new ESP32-C3 | Andreas Spiess

RISC-V: How much is open source? Featuring the new ESP32-C3 | Andreas SpiessWhen I got these new RISC-V ESP32 boards in my mail, I asked myself: Is this new technology revolutionary as written everywhere? What are the…

RISC-V Becoming Less Risky with the Right Verification

RISC-V Becoming Less Risky with the Right VerificationRISC-V continues to make headlines across the electronic design industry. You may have seen the recent news that the OpenHW Group is delivering their first…

Developing Diosix: An open-source RISC-V bare-metal hypervisor from scratch in Rust | British Computer Society Open Source Specialists

Developing Diosix: An open-source RISC-V bare-metal hypervisor from scratch in Rust | British Computer Society Open Source SpecialistsDiosix bridges two interesting and emerging worlds of technology: Rust and RISC-V. As a bare-metal, type-1 hypervisor, Diosix strives to bring the security, reliability, and…

Expanding a RISC-V Processor with Vector Instructions for Accelerating Machine Learning | British Computer Society Open Source Specialists

Expanding a RISC-V Processor with Vector Instructions for Accelerating Machine Learning | British Computer Society Open Source SpecialistsPresented by Pete Alexander, John Holden, Harry Cooper, Byron Theobald, Aaryaman Bhattacharya, Matthew Johns, University of Southampton The open-source RISC-V instruction set architecture is gaining…

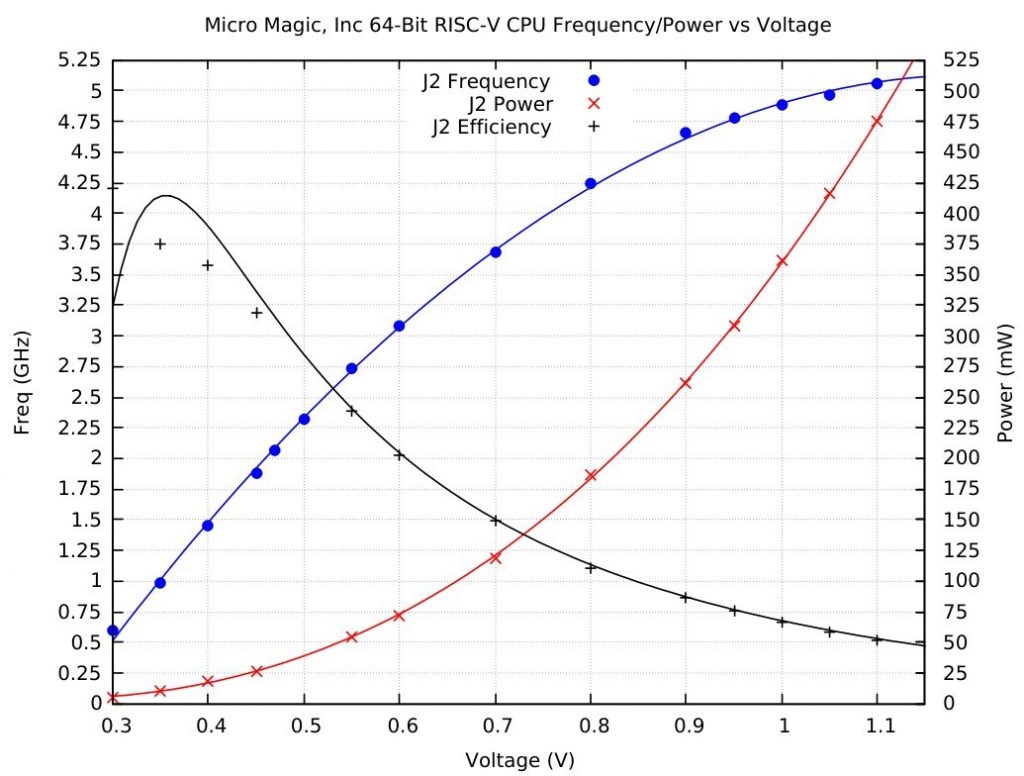

Micro Magic, Inc. Delivers Ultra Low Power 64-Bit RISC-v Core | Cision PR Newswire

Micro Magic, Inc. Delivers Ultra Low Power 64-Bit RISC-v Core | Cision PR NewswireSUNNYVALE, Calif., Feb. 12, 2021 /PRNewswire/ -- Today, Micro Magic, Inc. announced its Ultra Low power 64-bit RISC-V core consuming only 10mW at 1Ghz. Micro Magic's design techniques allow…

RISC-V Awareness Webinar From Dr. Ali Ahmed and Zeeshan Rafique from UIT | Micro Electronics Research Lab -UIT

RISC-V Awareness Webinar From Dr. Ali Ahmed and Zeeshan Rafique from UIT | Micro Electronics Research Lab -UITThis webinar was arranged to bring awareness and to tell the importance of RISC-V to Pakistani students. This presentation includes: RISC-V introduction RISC-V achievements globally…

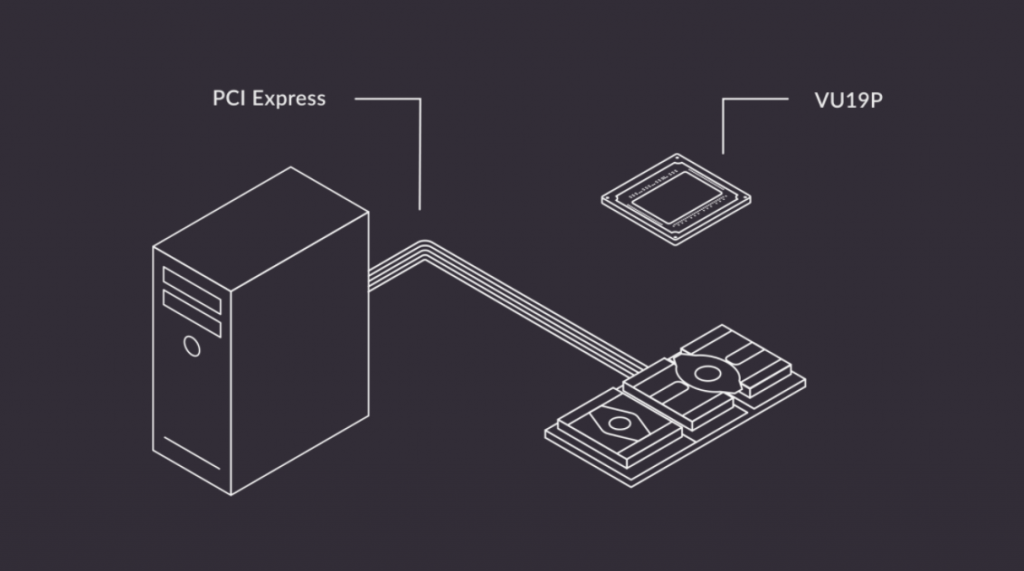

High-throughput open source PCIe on Xilinx VU19P-based ASIC prototyping platform

High-throughput open source PCIe on Xilinx VU19P-based ASIC prototyping platformOriginally published by Antmicro In the daily work at Antmicro, they use FPGAs primarily for their flexibility and parallel data processing capabilities that make…

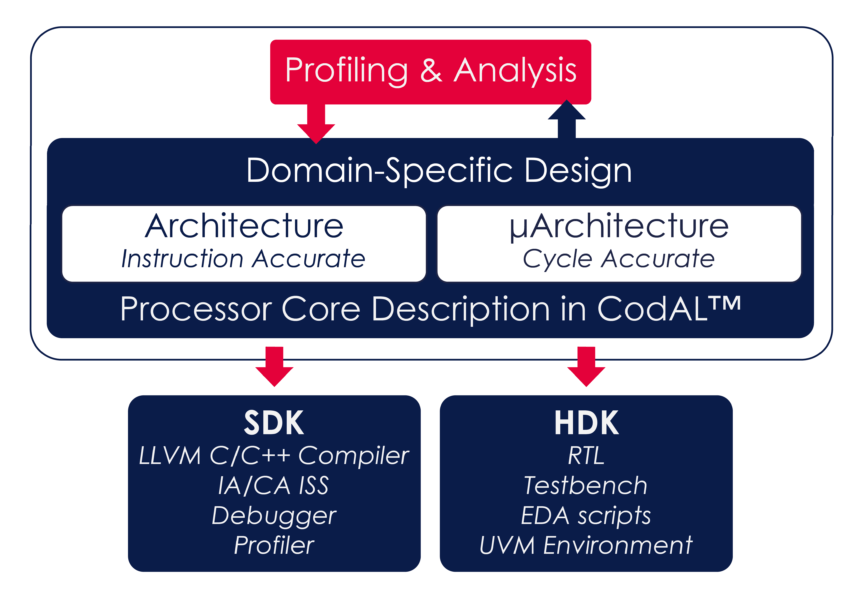

CUSTOMIZING AN EXISTING RISC-V PROCESSOR | Codasip

CUSTOMIZING AN EXISTING RISC-V PROCESSOR | CodasipIn the previous post, we considered how you could create an optimized ISA for a domain-specific processor core by profiling software and experimenting with adding/removing instructions.…

India's First Indigenous Microprocessor! The SHAKTI Processor Program, was started as an academic initiative back in 2014 by the Reconfigurable Intelligent Systems Engineering (RISE) group…

為協助台灣產業邁入AIoT(人工智慧+物聯網)時代,並從嵌入式CPU開放架構切入商用市場,由「台灣物聯網產業技術協會」黃崇仁理事長倡議,與力晶、智成、神盾、晶心、聯發科、瑞相、力積電、力旺、嵌譯等發起企業協助下,「台灣RISC-V聯盟」於108年3月7日舉辦啟動儀式,並邀請經濟部、科技部與台、清、交大多位教授到場見證。 「台灣RISC-V聯盟」成立主要目的,是希望透過產、學、研三方合作方式,共同協助將RISC-V開放架構導入台灣,並串聯海內外RISC-V生態系資源,讓台灣產業從研發、設計到應用,都能具備AIoT整合能力,並搭上5G通訊趨勢與商機,進而提升台灣產業競爭力。 RISC-V開放架構可以讓廠商快速開發新應用,尤其對於新創業者來說,不僅能在開發階段省下授權費用,也能依照自己需求增加專屬指令集,而不受限制原始授權限制,所以這是台灣科技產業的新機會,敬邀大家一同參與加入「台灣RISC-V聯盟」。 In order to help Taiwan’s industry enter the AIoT (artificial intelligence + Internet of Things) era, and cut into the commercial market…

The post Luke Hakes, Octopus Ventures: The end of our 10 year journey appeared first on UltraSoC.]]>

The post Chris Wade maps out UltraSoC’s development appeared first on UltraSoC.]]>

The post A parting view from the Chair: Alberto Sangiovanni-Vincentelli appeared first on UltraSoC.]]>