64-bit CPU with RISC-V Vector Extension | Design & Reuse

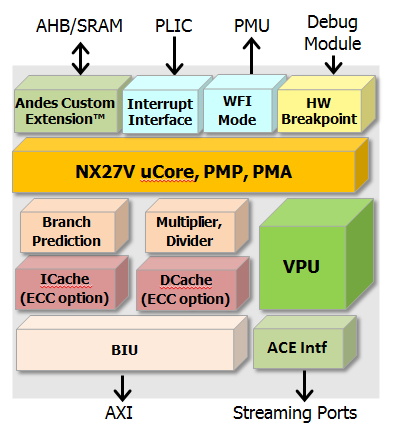

64-bit CPU with RISC-V Vector Extension | Design & ReuseThe 64-bit NX27V is a vector processor with 5-stage scalar pipeline that supports the latest RISC-V specification, including the IMAFD standard instructions, “C” 16-bit compression…

What is RISC-V? (2021) | Learn Technology in 5 Minutes | Makerdemy

What is RISC-V? (2021) | Learn Technology in 5 Minutes | MakerdemyRISC-V is an Instruction set architecture developed at UC Berkeley. Many startups and tech giants have noticed this technology because it is totally free and…

Imperas Leads The RISC-V Processor Verification Ecosystem | Imperas

Imperas Leads The RISC-V Processor Verification Ecosystem | ImperasOxford, UK – January 25th, 2021 – Imperas Software Ltd., the leader in RISC-V processor verification technology, today announced the latest addition to the Imperas RISC-V Verification…

RISC-V continues to make headlines across the electronic design industry. You may have seen the recent news that the OpenHW Group is delivering their first…

Embedded Trends and Tech to Watch in 2021 | Shawn Prestridge, Electronic Design

Embedded Trends and Tech to Watch in 2021 | Shawn Prestridge, Electronic Design2021 will be a breakout year for RISC-V. We’ve seen R&D groups at large customers dabble with RISC-V to see if they want to base…

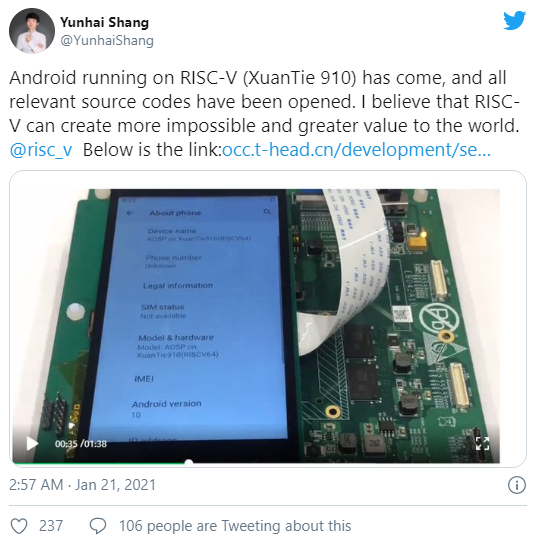

Android 10 ported to RISC-V board powered by Alibaba T-Head XuanTie C910 Processor | Jean-Luc Aufranc, CNX Software

Android 10 ported to RISC-V board powered by Alibaba T-Head XuanTie C910 Processor | Jean-Luc Aufranc, CNX SoftwareRISC-V has made a lot of progress in just a few years, but for anything requiring 3D graphics acceleration, it’s not quite there yet. and we…

Overview of Diplomacy for writing effective hardware design language Chisel (Japanese)

Overview of Diplomacy for writing effective hardware design language Chisel (Japanese)ハードウェア記述言語Chiselをもっともっと活用するためのDiplomacy概説 発表者:msyksphinz (FPGA開発日記著者) @msyksphinz_dev https://msyksphinz.hatenablog.com Chisel使ってますか? Scalaをベースとしたハードウェア構築言語. 高位合成言語ではない SiFiveのRISC-V IPで採用されている Rocket-Chip : https://github.com/chipsalliance/rocket-chip BOOM : https://github.com/riscv-boom/riscv-boom Chiselの基礎 : 「Chiselを始めたい人に読んで欲しい本」 https://nextpublishing.jp/book/12162.html ChiselがVerilogを生成するまで ChiselはScalaのDSLなので、Chisel CompilerはScalaで記述してある Chisel CompilerはFIR (Flexible Interpretation Representation)と呼ばれる中間言語を生成する…

The Android system on RISC-V has come!| Open Chip Community

The Android system on RISC-V has come!| Open Chip CommunityThe Android system on RISC-V has come! T-Head has ported Android 10 on RISC-V architecture. Android's primary purpose is to create an open software platform…

Android 10 ported to homegrown multi-core RISC-V system-on-chip by Alibaba biz, source code released | Matthew Hughes, The Register

Android 10 ported to homegrown multi-core RISC-V system-on-chip by Alibaba biz, source code released | Matthew Hughes, The RegisterAlibaba-owned T-Head Semiconductor says it has ported Android 10 to its own RISC-V chips, highlighting increased momentum for the open-source instruction set architecture (ISA) against…

Antmicro Joins the EC’s VEDLIoT Project to Bring Ultra-Efficient RISC-V Deep Learning to the IoT | Gareth Halfacree, hackster.io

Antmicro Joins the EC’s VEDLIoT Project to Bring Ultra-Efficient RISC-V Deep Learning to the IoT | Gareth Halfacree, hackster.ioOpen source silicon pioneer Antmicro has announced its involvement in the European Commission's Very Efficient Deep Learning in Internet of Things (VEDLIoT) project, with the…

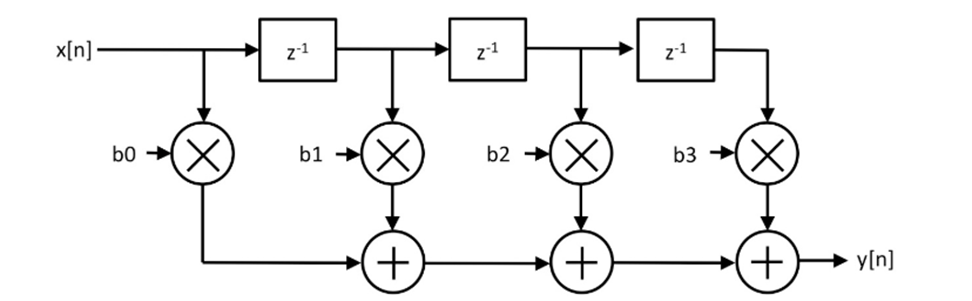

RISC-V CPU Performance | Maven Silicon

RISC-V CPU Performance | Maven SiliconThis video explains how Maven Silicon measures the CPU performance and how we try to improve the processor performance by improving its clock frequency and…

The Future Is Now: Mark Himelstein of RISC-V On How Their Technological Innovation Will Shake Up The Tech Scene | Fotis Georgiadis, Authority Magazine

The Future Is Now: Mark Himelstein of RISC-V On How Their Technological Innovation Will Shake Up The Tech Scene | Fotis Georgiadis, Authority MagazineSome of the greatest “rocket science” in RISC-V is the simplicity, elegance, and flexibility of it. While some of the individual pieces are not “rocket…