I’m heading to SC25 in St. Louis next week to advocate for the growing role of RISC-V in high-performance computing (HPC), alongside my peers in the RISC-V HPC special interest group (SIG).

High Performance Computing (HPC) is the powerhouse behind a wide range of scientific discoveries and engineering solutions. However, times never stand still as users demand the ability to model ever larger, more complex, and more varied workloads at reduced time-to-solution.

In parallel, there is growing emphasis on decarbonisation and improving sustainability of HPC operations; you will no doubt have seen news stories about how much carbon is emitted by a data center.

I believe RISC-V has the potential to deliver real value as we confront these grand challenges. The flexibility offered by the open and modular nature of the RISC-V open standard enables vendors to develop far more specialised hardware solutions than are currently available in the mainstream.

RISC-V is a unique, open, and community-driven building block for HPC; without RISC-V it would not be possible to even entertain the idea of a fully open ecosystem due to the proprietary nature of other solutions.

Indeed, we have recently seen several RISC-V vendors release hardware that is HPC-capable, demonstrating that such specialisation can deliver performance and energy benefits over and above incumbent technologies.

That’s why my peers and I in the RISC-V HPC special interest group (SIG) are heading to SC25 in St. Louis next week to advocate for the growing role of RISC-V in high-performance computing. The SuperComputing (SC) conference is the world’s largest HPC conference, with around 20,000 attendees and the latest technology exhibitions, research papers, workshops, panels and community sessions.

This year, we will be hosting a workshop on RISC-V for HPC (Monday 17th of November), as well as a panel on openness and open standards on the afternoon of Thursday 20th.

Building on the Foundations of Our Previous RISC-V for HPC Events

One of the activities of the RISC-V HPC special interest group (SIG) is to drive adoption of RISC-V in HPC, raising awareness in the community and acting as a mouthpiece for the latest developments in the field.

This all started with ‘Birds of a Feather’ community building sessions in 2022. Since 2023 we have held workshops at SC and ISC High Performance (the latter being Europe’s largest HPC conference), as well as branching out in 2024 to HPC Asia and into India for HiPC later this year.

We have seen these events grow significantly in the past couple of years, with more high quality papers year-on-year exploring the current state of the art in RISC-V.

Our most recent workshop, held at ISC in the summer, saw RISC-V International CEO Andrea Gallo deliver a keynote about priorities for RISC-V and the progress that is being made, followed by a range of research which explored accelerating HPC codes on RISC-V accelerators and optimisation for RISC-V-based CPUs.

Having a Conversation with the Community

While the workshops are great, they have grown into full-on sessions and there isn’t always an opportunity to have a discussion with the wider audience. This is where the community Birds of a Feather (BoF) sessions really come in, which involve several RISC-V experts putting forward a position and then debating this with the audience.

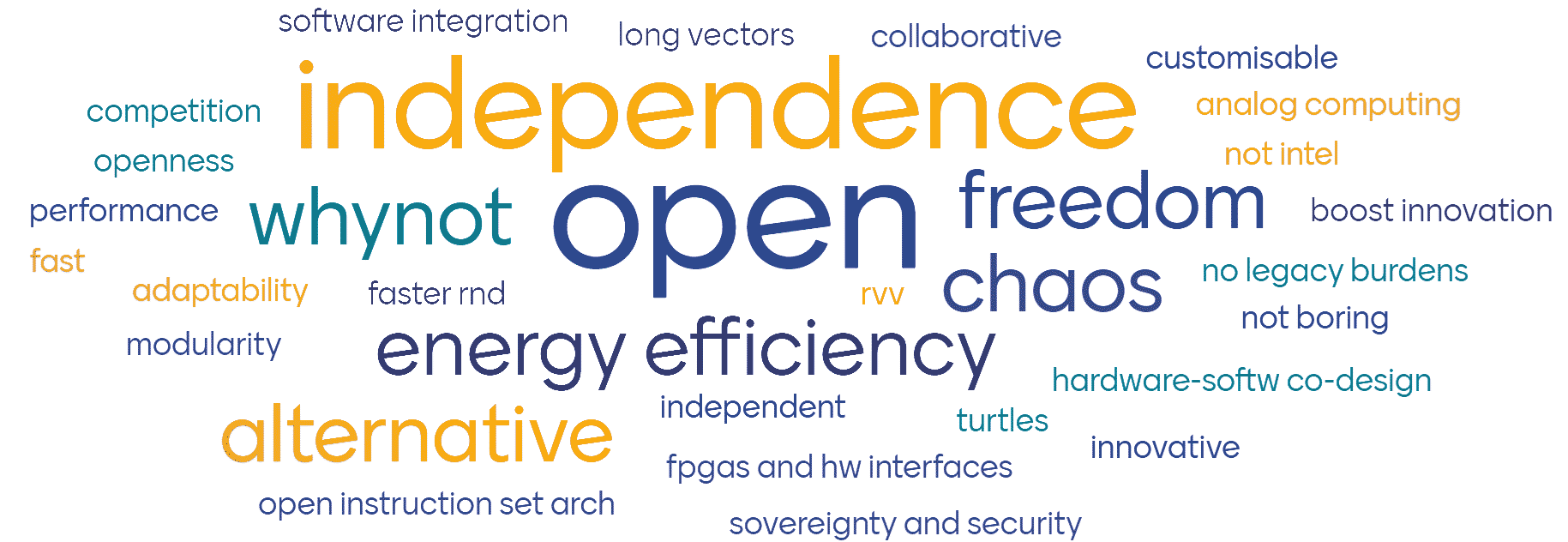

The most recent of these was at ISC this summer, and we began the session asking the audience to highlight why they felt RISC-V could benefit HPC. The word cloud below comprises the answers given, with the most popular highlighting the open and independent nature of the standard.

The most recent BoF session highlighted some of the predictions made in preceding years and explored whether these had come true or not; both in terms of what the experts felt but also enabling the audience to vote. Overall, the audience felt that RISC-V was meeting expectations in terms of overall growth and open source software tooling, but there was still work to be done in supporting the wider HPC ecosystem.

The most recent BoF session highlighted some of the predictions made in preceding years and explored whether these had come true or not; both in terms of what the experts felt but also enabling the audience to vote. Overall, the audience felt that RISC-V was meeting expectations in terms of overall growth and open source software tooling, but there was still work to be done in supporting the wider HPC ecosystem.

RISC-V at Supercomputing 2025

Last year at SC24, we upgraded to a full panel featuring representatives from RISC-V vendors, RISC-V International, and researchers. Participants highlighted their views on what RISC-V can offer to HPC. This active session covered a wide set of questions from the audience – ranging from those already working with RISC-V to those seeking more reassurance of RISC-V’s role in HPC.

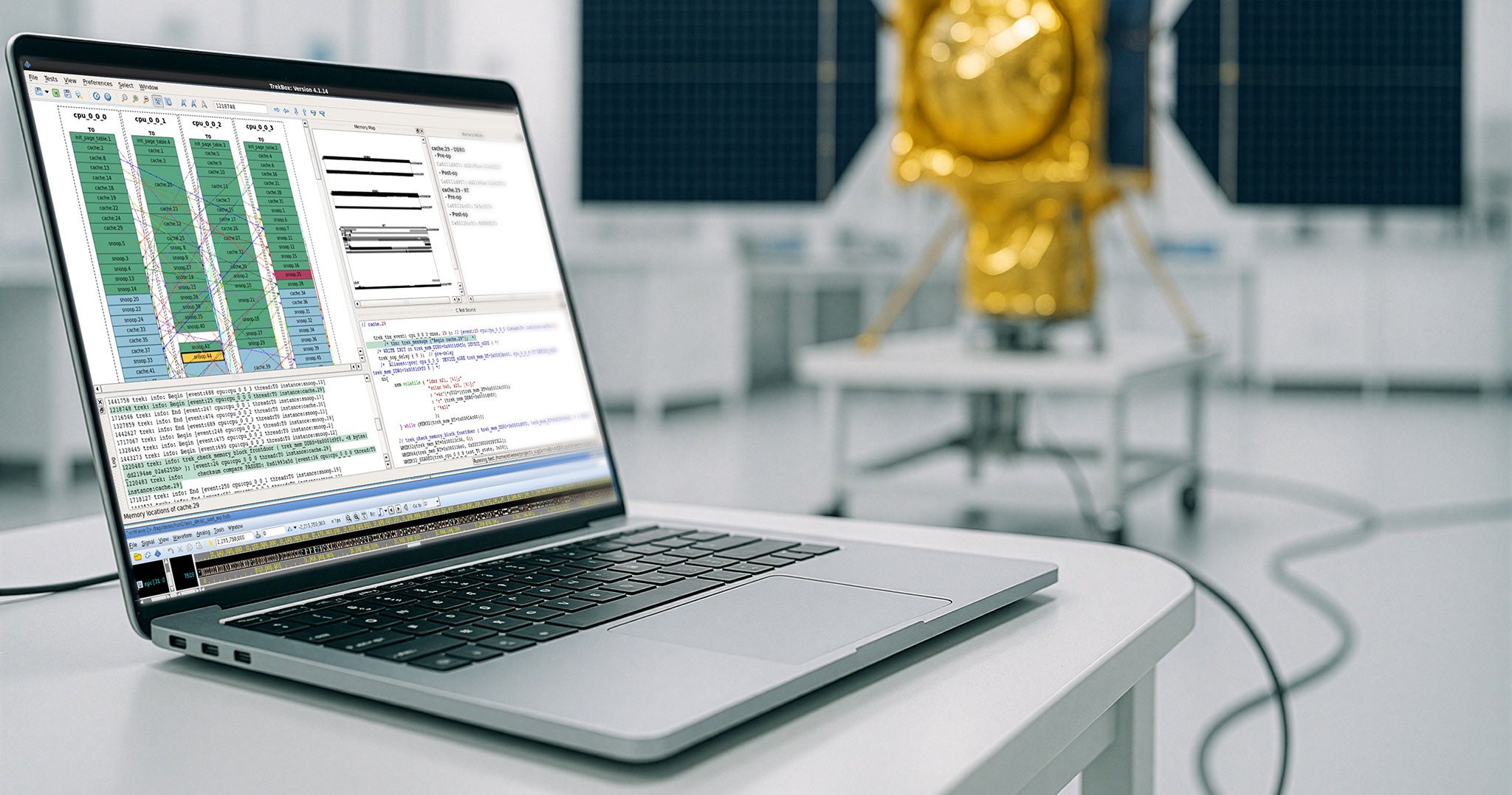

This year at SC25 in St. Louis, we will continue the conversation with the HPC community around RISC-V. We have a busy half-day workshop, running on Monday 17th from 9:00am to 12:30pm in room 242, starting with a keynote by Senior Fellow at Condor Computing, Shashank Nemawarkarl, who is responsible for the architecture and performance of Condor’s RISC-V processors.

This is then followed by five full research paper presentations, and a further five short presentations. Each of these covers a different aspect of the current state of the art in RISC-V for HPC, such as the use of accelerators, performance on new HPC class RISC-V CPUs, coupling with custom compute for RISC-V, libraries and tools for RISC-V on HPC, and more general developments in the RISC-V software ecosystem. It promises to be a busy and engaging session, with something for everybody.

If you’re attending SC25, workshop details can be found here: International Workshop on RISC-V for HPC (RISCVHPC) and all research papers will be published in the workshop proceedings.

We are also hosting a panel session on Thursday afternoon from 1:30pm to 3pm in rooms 231-232. This will explore whether a fully open, community-driven HPC ecosystem is a realistic proposition.

The purpose of this session is to take a full stack view around openness, highlighting where different open standards and activities can interplay. RISC-V is one of the key enablers here, providing openness at the Instruction Set Architecture (ISA) level downwards, with the session also exploring the role of open source software in HPC and key HPC tools and technologies that would benefit from being opened up.

Attendees can find the panel session details here: A Fully Open, Community-Driven HPC Ecosystem: A Credible Future or Chimera?

And if you’re not attending SC25, you can still hear from me exactly why I believe RISC-V has a strong future in HPC, some of our recent successes and the challenges still to come, by watching my talk at RISC-V Summit North America 2025: