This October 22–23, RISC-V Summit North America 2025 will bring the global RISC-V community together in Santa Clara for two packed days of keynotes, technical sessions, workshops, and an expo floor buzzing with demos. If open standard hardware is (or could be) your thing, this is your chance to be in the room where it happens.

If there was ever an example of RISC-V’s place at the heart of modern computing, this is it. Just look at who’s confirmed to take center stage so far: Clayton Turner, Director of NASA’s Langley Research Center; Martin Dixon, Engineering Director at Google; alongside trailblazers like RISC-V founder Krste Asanović and Microchip’s Ted Speers and a host of well-known faces from across the global community.

But RISC-V Summit North America isn’t just about sitting and listening. An architecture built on open standards thrives on open discussion. From panel discussions to workshops, poster presentations to our extensive exhibition hall and developer zone, we’re bringing the ecosystem together in Santa Clara to network, share breakthroughs, swap ideas, and shape the next wave of silicon innovation.

Keynote Speakers

We’re excited to announce our initial keynote speaker roster for 2025. You can view the full list here, and we’ll be adding more names as they’re confirmed.

We’re excited to announce our initial keynote speaker roster for 2025. You can view the full list here, and we’ll be adding more names as they’re confirmed.

| Martin Dixon, Google | Martin is an Engineering Director at Google Cloud. His team focuses on building the most efficient and highest-performance silicon for Google’s cloud customers. Martin’s background is in CPU and SoC architecture. He holds more than 50 patents in these areas.Martin will be talking about what’s needed for us to pave the road to datacenter-scale RISC-V chips, and how AI was used to automate the complex porting of Google’s software stack from x86 to RISC-V. |

| Clayton P. Turner, NASA | As Associate Administrator for the Space Technology Mission Directorate (STMD), Clayton is a 30-year NASA veteran – and today oversees the enablement of critical space-focused technologies.NASA is pioneering RISC-V for spacecraft autonomy, safety, and performance—so you can rest assured, this session will be a real moonshot. |

| Ted Speers, Microchip | Ted Speers is a Microchip Technical Fellow guiding FPGA product architecture and roadmaps, longtime RISC-V International board leader globally, and co-inventor on 35 U.S. patents.Microchip is using RISC-V to build what legacy ISAs cannot: purpose-built, certifiable, and mission-ready platforms. Ted will be following NASA’s Clayton P. Turner in sharing how we go about securing this final frontier. |

| Krste Asanović, SiFive | RISC-V’s Founder and Chief Architect is currently director of the UC Berkeley ASPIRE lab, tackling the challenge of improving computational efficiency now that transistor scaling is ending.Krste will offer an overview of RISC-V adoption across computing markets from Embedded to AI, outlining the programs within the ecosystem that will drive accelerating success for the RISC-V ISA. |

| Jérémy Dahan, AWS | Jérémy will examine how AWS’s infrastructure enables developers to instantly access RISC-V development environments through services like EC2 and F2 instances for FPGA-based development, and cloud-based emulation platforms.With real-world examples of this cloud-first approach, he’ll explore how democratized access is accelerating innovation cycles, reducing costs, and enabling organizations of all sizes to participate in RISC-V design and prototyping. |

| Daniela Barbosa, LF Decentralized Trust | Daniela serves as General Manager of Decentralized Technologies at the Linux Foundation and Executive Director of LF Decentralized Trust.Daniela will be sharing groundbreaking research at the intersection of RISC-V, Cryptography, and Blockchain – from proposals to re-imagine Ethereum’s execution layer with RISC-V to its growing role in zero-knowledge proof systems. |

| Dr Nick Brown, Senior Research Fellow, EPCC | Dr Nick Brown is Senior Research Fellow at EPCC, University of Edinburgh, coordinating exascale software initiatives and chairing the RISC-V International HPC SIG. He leads research in novel hardware, compilers, libraries, and programming models.In his keynote, Nick will share the latest advances in RISC-V-powered high performance computing (HPC). |

| Makeljana Shkurti, Chair of the RISC-V AI Market Development Committee & Ed Doran, VP of Strategy, Edge AI Foundation | Edge AI represents the fastest-growing demand for intelligence, where inference must happen close to the data, under tight cost, power and latency constraints. RISC-V is the only modular platform designed to meet these demands, enabling domain-specific acceleration from the smallest devices to the largest systems.In this joint Keynote, Ed Doran and Makeljana Shkurti will share how the growth of Edge AI and RISC-V innovation are not happening in parallel but rather sharing the same trajectory.Together, they will present a vision for the future of AI infrastructure – one where inference at the edge is efficient, sustainable and accelerated by RISC-V. |

Panel Sessions

The RISC-V ecosystem thrives on collaboration and open dialogue, and panel sessions embody that spirit. They bring together leaders from across industries to exchange ideas, challenge assumptions, and spark new directions. These conversations highlight how openness and shared expertise accelerate progress and strengthen the foundation of RISC-V as an open standard.

This year’s panel sessions include:

Linux and RISC-V: Principles for a Winning Partnership

Barna Ibrahim, RISE; Steve Wanless, Red Hat; Gordan Markus, Canonical; Brent Schroeder, SUSE

This panel explores the journey from no Linux distribution support to multiple major vendors targeting RISC-V—showing how open collaboration between RISC-V International, RISE, and the Linux ecosystem is building a stronger future.

Wednesday, October 22, 2025 | 4:50–5:30pm PT

Winning the Future of RISC-V Automotive MCU Through Ecosystem Collaboration and Open Standards

Brandy Goolsby, Vector; Dan Mender, Green Hills; Rolf Kühnis, Lauterbach; Rich Collins, Synopsys; Chris Thibeault, Infineon Technologies

Infineon and its partners will discuss how open standards and ecosystem collaboration are enabling a new generation of RISC-V automotive MCUs, showing the power of partnership to drive innovation in safety-critical domains.

Thursday, October 23, 2025 | 4:15–5:00pm PT

Why Should I Attend?

Whether you’re a chip designer, software developer, VC startup, or global tech leader, there’s something for you at RISC-V Summit North America 2025. We live in a world of remote calls and virtual meetups, but there’s still no substitute for being in the same room. That’s why the Summit matters:

- Collaboration is faster face-to-face. An expo hall demo or quick hallway chat can resolve what would take weeks over email.

- Inspiration is contagious. Hearing pioneers speak, seeing demos live, sharing meals — it all fuels your own ideas.

- Connections are stronger. A handshake and shared conversation builds trust in a way that Zoom simply can’t.

If you care about where open computing is headed, RISC-V Summit North America 2025 is the place to be. Don’t just read the coverage afterwards — help us shape it.

And if you’re new to the RISC-V ecosystem and don’t know where to start, join us on Tuesday, October 21st at 9 am for RISC-V 101: A free session featuring RISC-V International CEO Andrea Gallo and Jeffrey Osier-Mixon, Senior Principal Community Architect within the Office of the CTO at Red Hat.

Whether you’re curious about RISC-V or looking to deepen your understanding, it’ll give you a solid grounding in the ISA before heading into the main Summit. Registration is separate from the RISC-V Summit and can be completed here.

Summit Tracks

The RISC-V Summit North America is structured around dedicated tracks, each focusing on a core area of the ecosystem. This format ensures you can dive deep into the topics most relevant to your role, helping you maximize learning, networking, and value from every session throughout the event. You can build and track your own agenda in the Sched app.

|

Artificial Intelligence (AI): Discover how RISC-V unlocks AI, from tiny edge devices to powerful accelerators, with strategies to differentiate and scale. We’ve built this track for chip and system architects, ML engineers, software leads, and product owners shaping AI roadmaps. |

|

Datacenter / HPC: Move workloads faster and cheaper on open platforms. This track shares the latest on RISC-V servers, accelerators, and ecosystem readiness – as well as the latest HPC and supercomputing research from academia. It’s ideal for CTOs, platform owners, hyperscalers, OS vendors, and researchers driving cloud or supercomputing strategy and technology. |

|

Design and Verification: Turn ideas into silicon with confidence. Learn proven flows, best practices, and war stories that de-risk schedules and raise quality. Targeted at RTL designers, DV leads, EDA partners, and program managers chasing first-silicon success. |

|

Global Adoption: See how organizations and countries are scaling with RISC-V: strategies, case studies, and partnership models you can reuse. Perfect for executives, policymakers, investors, and program leaders building resilient supply chains and open computing initiatives. |

|

ISA and Processors: Get the inside track on the RISC-V ISA and next-gen cores: what’s shipping, what’s coming, and why it matters. CPU architects, implementers, contributors, and product planners making roadmap and investment decisions – this is the track for you. |

|

Security: Build trust from silicon to software. This track spotlights secure design patterns, memory safety techniques (CHERI), and certification paths for real products. We’ve geared this track towards security architects, firmware leaders, auditors, and CISOs responsible for safety, compliance, and resilience. |

|

Software: Bring your stack to life on RISC-V. Learn the state of kernels, toolchains, libraries, and containers—plus the practices that speed porting and performance. Suited to maintainers, distro builders, SDK teams, app developers, and DevOps. |

RISC-V Developer Workshops

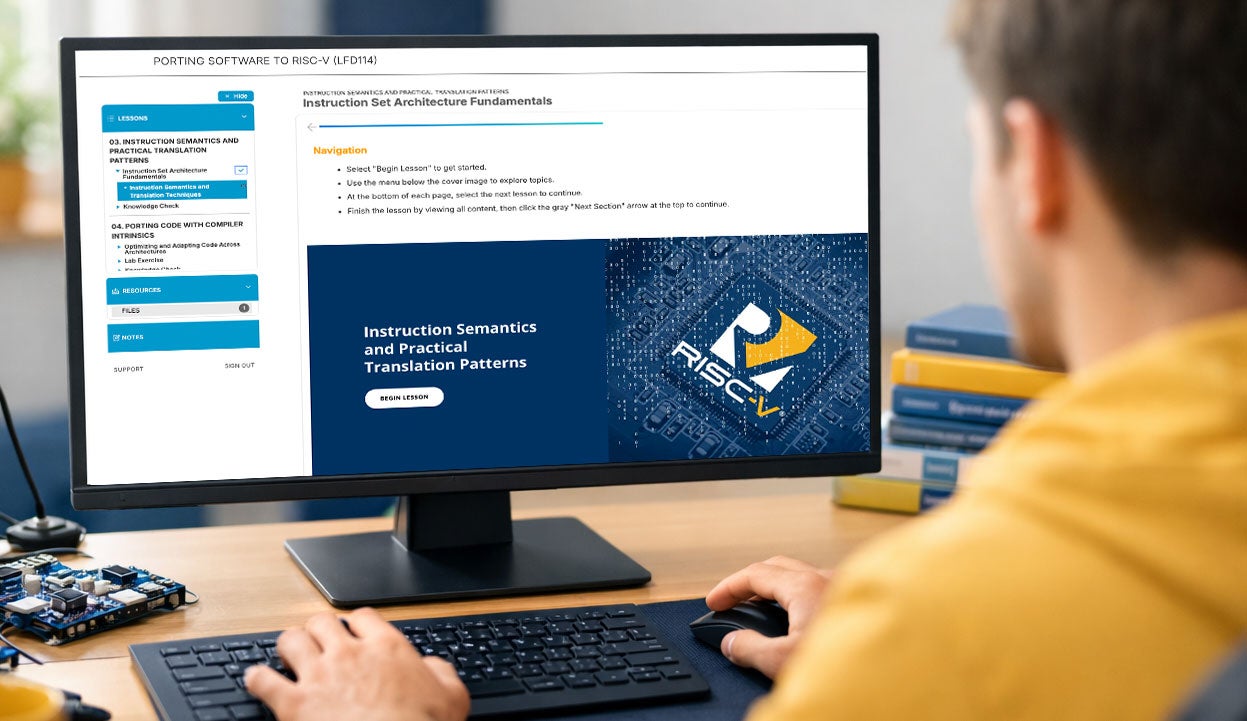

On Wednesday, October 22, 2025, hands-on developer workshops run alongside the summit as a separately ticketed program. Two concurrent tracks—hardware and software—deliver expert-led labs, practical guidance, and access to instructors you won’t find anywhere else.

Whether you’re architecting silicon or tuning toolchains, you’ll leave with working knowledge and reproducible artifacts.

Highlights include:

- Designing a RISC-V application processor

- Verifying your RISC-V application processor

- Optimizing designs for FPGAs

- Porting software to RISC-V hardware

- Optimizing software for RISC-V Vector (RVV)

- Building Yocto images

Capacity is limited to keep sessions intimate, so reserve a seat early to guarantee instructor attention and bench time. Learn more about our developer workshops here.

Join us at RISC-V Summit North America 2025 to learn more about RISC-V hardware, software, systems, development tools, security and much more. Registration is open now!