The first RISC-V Annual Report hit virtual shelves this week. Inside, it details a defining year for RISC-V, the open standard ISA I co-founded back in 2010. We share major technical milestones, accelerating industry adoption, global ecosystem growth, and how we’ve laid foundations for the next phase of commercial deployment.

You’ll find me on page 10 of the report, delivering the same consistent message to audiences at RISC-V Summits around the world: The State of the Union Is Strong.

By ‘union’, I refer to the RISC-V ecosystem: its contributors, users, and developers, from multi-national corporations to solo academics, working together under a shared banner to strengthen the standard and deliver real, functioning systems.

Now, it’s time for this union to demonstrate to vertical markets old and new that in 2026, its state isn’t just strong: it’s stronger than ever.

Workload-Specific Chips

For much of the RISC-V ISA’s first decade, “strong” largely meant momentum in establishing RISC-V as a generic, common ISA, supported by foundational software. Compilers, linkers, and toolchains that allowed binaries to run across many devices (the vast majority of those devices being embedded).

Yet even early on, we recognized that RISC-V’s long-term success would stem from enabling higher-value, workload-specific systems in markets where one size rarely fits all. From the outset, RISC-V was designed to be modular, allowing innovation in one domain to be reused in another. That reuse, built on a shared base ISA and common software foundations, is one of the main reasons RISC-V has been able to evolve so quickly.

Beyond that common, shared base, each industry vertical requires its own tuned software stack, hardware extensions and ecosystem. Broad adoption requires more than convincing decision-makers that they ‘need’ RISC-V.

It takes deep, sustained effort to identify gaps, coordinate partners, and implement complete solutions. It’s far more important to deliver 100% of what a few verticals need than delivering only 90% of many more.

At RISC-V International, this work happens through special interest groups (SIGs) and task groups (TGs). The challenge is not simply building software for a vertical, but doing so in a way that preserves coherence across the broader ecosystem. Leveraging shared components while allowing specialization is what enables sustainable progress.

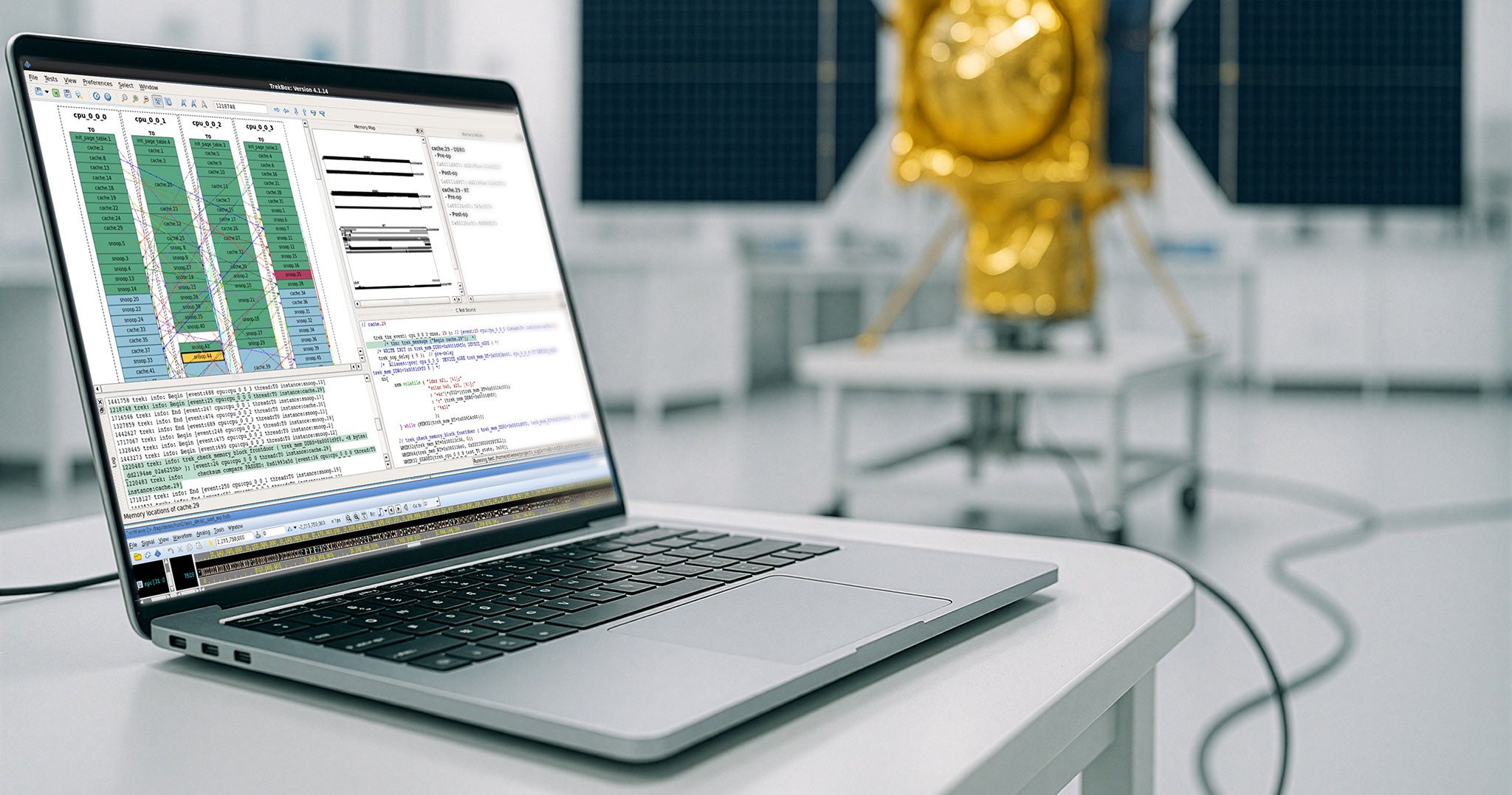

RISC-V is already making solid moves in key verticals, with momentum building across Automotive, expanding deployment options for Data Center infrastructure, growing credibility in High Performance Computing (HPC), accelerating adoption in IoT/Embedded designs, and proving its scalability for mission-critical Space and Aerospace systems.

Much of this momentum has been driven organically by our members. Building on years of work at the silicon, IP, and tools level, RISC-V International and its community have deliberately driven awareness higher up the value chain by engaging OEMs, integrators, and solution providers.

In 2025 we took that effort further, launching targeted campaigns that articulate how RISC-V’s unique characteristics address specific challenges in specific vertical markets. As a result, RISC-V is now firmly part of the vocabulary, roadmaps, and procurement choices of decision makers in key sectors.

The RISC-V Annual Report 2025 is live! Download it today and learn what made 2025 a defining year for the open standard ISA: major technical milestones, accelerating industry adoption, global ecosystem growth, and the foundations laid for the next phase of commercial deployment.