The Incredible Growth of RISC-V in India

The Incredible Growth of RISC-V in IndiaRISC-V is being adopted around the world as the silicon industry looks to the open RISC-V instruction set architecture (ISA) to offer a new level…

As part of CHIPS Alliance’s mission to enable a software-driven approach to silicon, working with Google and other CHIPS members, Antmicro has been developing and improving…

RISC-V Summit Europe 2023: Highlights from Barcelona

RISC-V Summit Europe 2023: Highlights from BarcelonaMore than 500 attendees, from across the world, attended the first-ever RISC-V Summit Europe Last month, the first-ever RISC-V Summit Europe happened in Barcelona, Spain.…

The Call for Papers for RISC-V Summit China 2023 is Open

The Call for Papers for RISC-V Summit China 2023 is OpenRISC-V Summit China is a major international event to share technical and business innovation around RISC-V. The global event brings together the community for a…

GreenRio: A Linux-Compatible RISC-V Processor Designed for Open-Source EDA Implementations

GreenRio: A Linux-Compatible RISC-V Processor Designed for Open-Source EDA ImplementationsSince 20 years ago, Intel has successfully developed the 3 GHz processor in 130nm process. However, as the design complexity of IC continues to increase,…

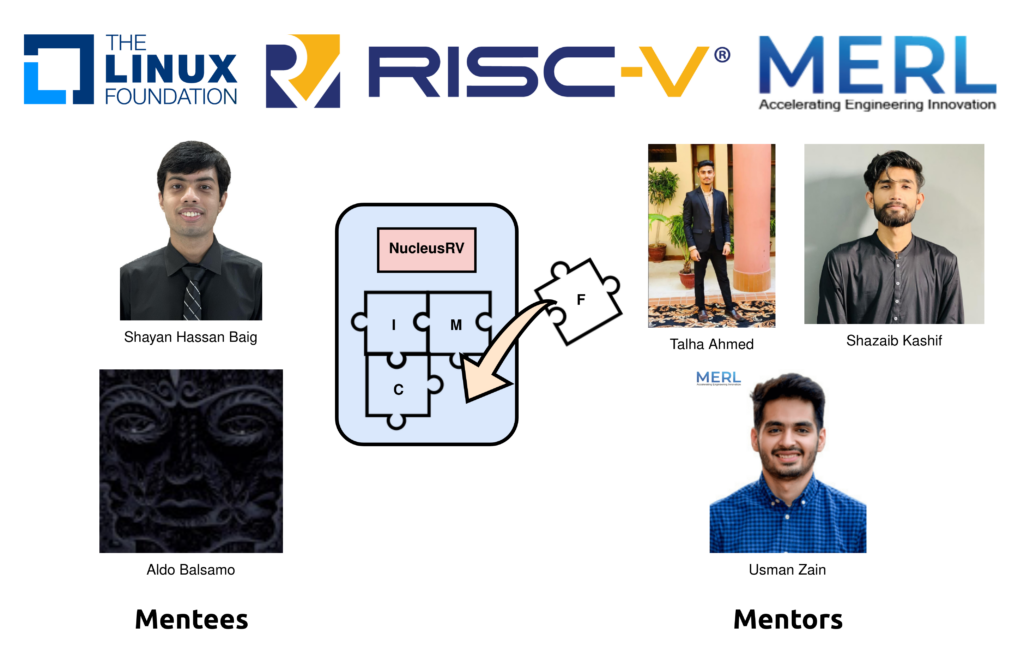

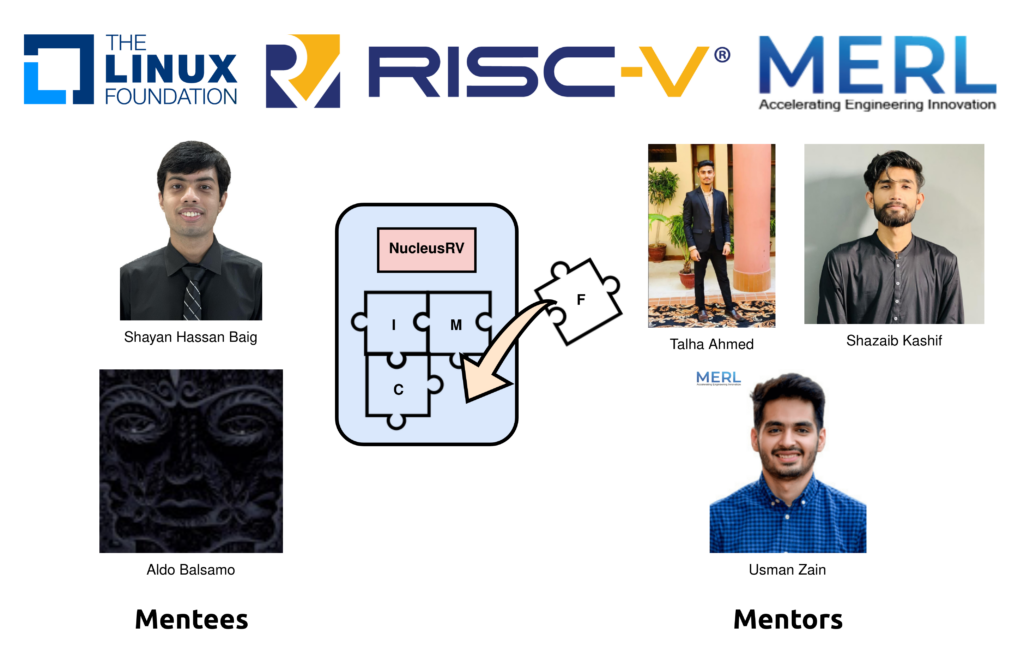

Addition of Single Precision Floating Point (F) extension in NucleusRV: RISC-V based RV32-IMC Core

Addition of Single Precision Floating Point (F) extension in NucleusRV: RISC-V based RV32-IMC CoreLinux Foundation Mentorship Spring 2023 at Micro Electronics Research Lab (MERL) sponsored by RISC-V International Abstract The goal of the project is to improve the…

When tapas meet tech: Barcelona’s RISC-V Summit feeds our appetite for innovation

When tapas meet tech: Barcelona’s RISC-V Summit feeds our appetite for innovationBy Brett Cline, Codasip Alright, let's talk about Barcelona. Now, you might be thinking of mouthwatering tapas, smooth local wines, and the pulsing life in…

Integrating Tile Link UH in the Caravan Framework: A Journey of Enhanced Functionality

Integrating Tile Link UH in the Caravan Framework: A Journey of Enhanced FunctionalityWe are thrilled to share the details of our recent project, where we successfully integrated Tile Link UH (Ultra High) into the Caravan framework. Tile…

Safety Critical Real-Time Operating System, SAFERTOS® Available With MiV_RV32 Soft CPU

Safety Critical Real-Time Operating System, SAFERTOS® Available With MiV_RV32 Soft CPUSAFERTOS® is a real-time operating system (RTOS) designed specifically for use in safety-critical systems. WITTENSTEIN high integrity systems is a Mi-V Ecosystem Partner of Microchip…

SOPHGO Donates 50 RISC-V Motherboards – Learn More About the Pioneer Box

SOPHGO Donates 50 RISC-V Motherboards – Learn More About the Pioneer BoxNew RISC-V International member SOPHGO is committed to the development and promotion of AI RISC-V CPU and other computing products. RISC-V member Milk-V delivers high-quality…

NOEL-V Processor’s Security Extensions for Safe and Secure Computing

NOEL-V Processor’s Security Extensions for Safe and Secure ComputingSafety and security are increasingly important aspects when designing computer systems, and work is carried out within RISC-V International technical groups to establish specifications that…

NOEL-V: A RISC-V Processor for High-Performance Space Applications

NOEL-V: A RISC-V Processor for High-Performance Space ApplicationsSpace applications pose significant challenges for electronic systems as they must contend with a myriad of environmental factors once they are launched. These factors include…

The Incredible Growth of RISC-V in India

The Incredible Growth of RISC-V in IndiaRISC-V is being adopted around the world as the silicon industry looks to the open RISC-V instruction set architecture (ISA) to offer a new level…

As part of CHIPS Alliance’s mission to enable a software-driven approach to silicon, working with Google and other CHIPS members, Antmicro has been developing and improving…

RISC-V Summit Europe 2023: Highlights from Barcelona

RISC-V Summit Europe 2023: Highlights from BarcelonaMore than 500 attendees, from across the world, attended the first-ever RISC-V Summit Europe Last month, the first-ever RISC-V Summit Europe happened in Barcelona, Spain.…

The Call for Papers for RISC-V Summit China 2023 is Open

The Call for Papers for RISC-V Summit China 2023 is OpenRISC-V Summit China is a major international event to share technical and business innovation around RISC-V. The global event brings together the community for a…

GreenRio: A Linux-Compatible RISC-V Processor Designed for Open-Source EDA Implementations

GreenRio: A Linux-Compatible RISC-V Processor Designed for Open-Source EDA ImplementationsSince 20 years ago, Intel has successfully developed the 3 GHz processor in 130nm process. However, as the design complexity of IC continues to increase,…

Addition of Single Precision Floating Point (F) extension in NucleusRV: RISC-V based RV32-IMC Core

Addition of Single Precision Floating Point (F) extension in NucleusRV: RISC-V based RV32-IMC CoreLinux Foundation Mentorship Spring 2023 at Micro Electronics Research Lab (MERL) sponsored by RISC-V International Abstract The goal of the project is to improve the…

When tapas meet tech: Barcelona’s RISC-V Summit feeds our appetite for innovation

When tapas meet tech: Barcelona’s RISC-V Summit feeds our appetite for innovationBy Brett Cline, Codasip Alright, let's talk about Barcelona. Now, you might be thinking of mouthwatering tapas, smooth local wines, and the pulsing life in…

Integrating Tile Link UH in the Caravan Framework: A Journey of Enhanced Functionality

Integrating Tile Link UH in the Caravan Framework: A Journey of Enhanced FunctionalityWe are thrilled to share the details of our recent project, where we successfully integrated Tile Link UH (Ultra High) into the Caravan framework. Tile…

Safety Critical Real-Time Operating System, SAFERTOS® Available With MiV_RV32 Soft CPU

Safety Critical Real-Time Operating System, SAFERTOS® Available With MiV_RV32 Soft CPUSAFERTOS® is a real-time operating system (RTOS) designed specifically for use in safety-critical systems. WITTENSTEIN high integrity systems is a Mi-V Ecosystem Partner of Microchip…

SOPHGO Donates 50 RISC-V Motherboards – Learn More About the Pioneer Box

SOPHGO Donates 50 RISC-V Motherboards – Learn More About the Pioneer BoxNew RISC-V International member SOPHGO is committed to the development and promotion of AI RISC-V CPU and other computing products. RISC-V member Milk-V delivers high-quality…

NOEL-V Processor’s Security Extensions for Safe and Secure Computing

NOEL-V Processor’s Security Extensions for Safe and Secure ComputingSafety and security are increasingly important aspects when designing computer systems, and work is carried out within RISC-V International technical groups to establish specifications that…

NOEL-V: A RISC-V Processor for High-Performance Space Applications

NOEL-V: A RISC-V Processor for High-Performance Space ApplicationsSpace applications pose significant challenges for electronic systems as they must contend with a myriad of environmental factors once they are launched. These factors include…