Exploring the RISC-V Summit 2024: Technical Sessions Announced

Exploring the RISC-V Summit 2024: Technical Sessions AnnouncedThe RISC-V Summit North America Plenary Sessions are now live on the event website. Each year, we are continually impressed with the high caliber of…

Trailblazers: Board of Directors Technical Award Winners 2024

Trailblazers: Board of Directors Technical Award Winners 2024By: Iris Zheng, Digital Marketing Intern, RISC-V International Five technical leaders were honored at RISC-V Summit Europe 2024 for their remarkable contributions to the RISC-V…

SpacemiT Key Stone K1 AI CPU has been adapted to the Fedora operating system successfully. With the Fedora operating system successfully running on the MUSE…

More than 1,300 Attendees Expected at RISC-V Summit China Next Week

More than 1,300 Attendees Expected at RISC-V Summit China Next WeekCheck out all the impressive talks and co-located events Next week, from August 21-23, more than 1,300 attendees will gather at the Huanglong Hotel in…

Microchip, and O.C.E. Technology deliver high-reliability RTOS for Polarfire® SoC FPGA space applications

Microchip, and O.C.E. Technology deliver high-reliability RTOS for Polarfire® SoC FPGA space applicationsBy: Barry Kavanagh, Chief Executive Officer, O.C.E. Technology Ltd. Polarfire® SoC FPGA RISC-V space applications can now take advantage of an RTOS compliant to ESA…

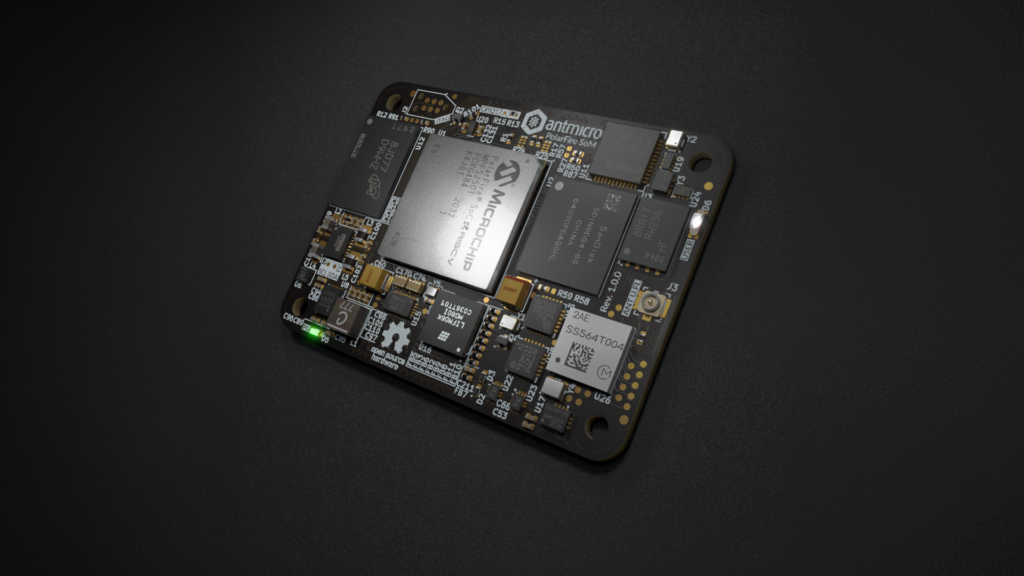

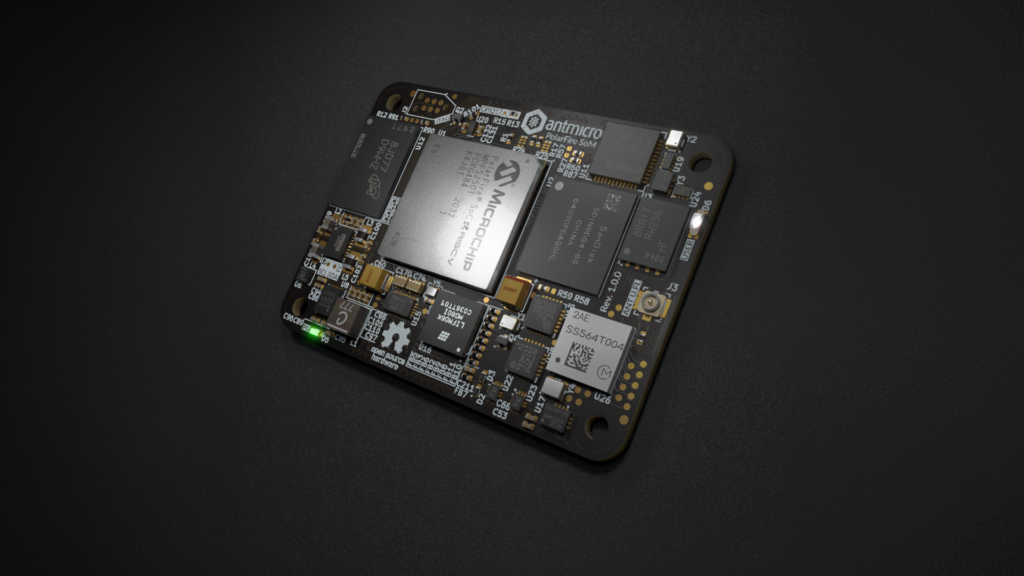

Open source System on Module with Microchip PolarFire SoC

Open source System on Module with Microchip PolarFire SoCThe PolarFire SoC was the world’s first Linux-enabled mass market multi-core RISC-V SoC, originally made available pre-silicon by Microchip through Antmicro’s Renode simulation framework. Thanks…

By: Antmicro The openness and customizability of the RISC-V ISA has encouraged its use across a variety of scenarios, such as supporting cores in larger…

Debugging of RISC-V-Based Chips Made Easy

Debugging of RISC-V-Based Chips Made EasyFROM SIMPLE MICROCONTROLLERS TO COMPLEX MULTICORE SOCS RISC-V cores can be found in increasingly more chips, either as the main CPU(s) or as a companion…

New Launch: Advanced RISC-V Courses | Maven Silicon

New Launch: Advanced RISC-V Courses | Maven SiliconBy: Maven Silicon We are delighted to inform you that we have recently published Advanced RISC-V Processor IP Design and Verification Online Courses. Our Founder and…

With Innovative technology, a collaborative spirit and a unique value proposition, Chip flow is setting itself to be the next generation of semiconductor solutions. Interview…

RT-Thread: Pioneering Real-Time Operating System for RISC-V

RT-Thread: Pioneering Real-Time Operating System for RISC-VIn the realm of modern computing architectures, the emergence of RISC-V marks a significant development, offering unprecedented openness and flexibility for processor design and implementation.…

July 1st, 2024 – The METASAT Project, a European Commission-funded initiative aimed at transforming satellite technology is pleased to announce significant progress after a year…

Exploring the RISC-V Summit 2024: Technical Sessions Announced

Exploring the RISC-V Summit 2024: Technical Sessions AnnouncedThe RISC-V Summit North America Plenary Sessions are now live on the event website. Each year, we are continually impressed with the high caliber of…

Trailblazers: Board of Directors Technical Award Winners 2024

Trailblazers: Board of Directors Technical Award Winners 2024By: Iris Zheng, Digital Marketing Intern, RISC-V International Five technical leaders were honored at RISC-V Summit Europe 2024 for their remarkable contributions to the RISC-V…

SpacemiT Key Stone K1 AI CPU has been adapted to the Fedora operating system successfully. With the Fedora operating system successfully running on the MUSE…

More than 1,300 Attendees Expected at RISC-V Summit China Next Week

More than 1,300 Attendees Expected at RISC-V Summit China Next WeekCheck out all the impressive talks and co-located events Next week, from August 21-23, more than 1,300 attendees will gather at the Huanglong Hotel in…

Microchip, and O.C.E. Technology deliver high-reliability RTOS for Polarfire® SoC FPGA space applications

Microchip, and O.C.E. Technology deliver high-reliability RTOS for Polarfire® SoC FPGA space applicationsBy: Barry Kavanagh, Chief Executive Officer, O.C.E. Technology Ltd. Polarfire® SoC FPGA RISC-V space applications can now take advantage of an RTOS compliant to ESA…

Open source System on Module with Microchip PolarFire SoC

Open source System on Module with Microchip PolarFire SoCThe PolarFire SoC was the world’s first Linux-enabled mass market multi-core RISC-V SoC, originally made available pre-silicon by Microchip through Antmicro’s Renode simulation framework. Thanks…

By: Antmicro The openness and customizability of the RISC-V ISA has encouraged its use across a variety of scenarios, such as supporting cores in larger…

Debugging of RISC-V-Based Chips Made Easy

Debugging of RISC-V-Based Chips Made EasyFROM SIMPLE MICROCONTROLLERS TO COMPLEX MULTICORE SOCS RISC-V cores can be found in increasingly more chips, either as the main CPU(s) or as a companion…

New Launch: Advanced RISC-V Courses | Maven Silicon

New Launch: Advanced RISC-V Courses | Maven SiliconBy: Maven Silicon We are delighted to inform you that we have recently published Advanced RISC-V Processor IP Design and Verification Online Courses. Our Founder and…

With Innovative technology, a collaborative spirit and a unique value proposition, Chip flow is setting itself to be the next generation of semiconductor solutions. Interview…

RT-Thread: Pioneering Real-Time Operating System for RISC-V

RT-Thread: Pioneering Real-Time Operating System for RISC-VIn the realm of modern computing architectures, the emergence of RISC-V marks a significant development, offering unprecedented openness and flexibility for processor design and implementation.…

July 1st, 2024 – The METASAT Project, a European Commission-funded initiative aimed at transforming satellite technology is pleased to announce significant progress after a year…