Recently, Lauterbach, a microprocessor development tool manufacturer, has implemented a new support for T-Head XuanTie processors. Its TRACE32® debugging tool now maintains the XuanTie 9 series, such as C906, E906, and other CPUs. This article introduces and describes further debugging and development on the XuanTie processors with TRACE32®.

TRACE32®

Lauterbach is one of the world’s largest producer of complete, modular, and upgradeable microprocessor development tools. Their expertise with in development of debuggers and real-time trace have remained a leading competitor in the industry since 1979. The TRACE32® product line supports technologies, such as JTAG, SWD, NEXUS, or ETM with embedded debuggers for software, as well as hardware trace. This support is the foundation for almost 100 cores deployed in over 5000 chip families, including ARC, Arm® Cortex®-A/-R/-M, Neoverse and Armv9, RISC-V®, Power Architecture®, TriCore™, RH850, and Xtensa®.

Key features of TRACE32® are:

- Heterogenous multicore debugging

- Trace-based profiling

- Debugging of complex systems

- Trusted tools for functional safety

- Open software APIs

- Early support for new developments

- Cutting-edge support

- Tools that grow to meet your challenges

Overview of the XuanTie Processor

The XuanTie processor IP covers a variety of scenarios from terminal to cloud. It is the cornerstone of intellectual and secure integrated chip architecture from the edge to cloud, providing a computing center for the digital age. XuanTie has been established in the independent development of proprietary core technologies since its establishment. Its new series of processors actively embrace open-source RISC-V architecture. The XuanTie processor IP is widely applied to computer, storage, industrial connection, network communication, smart home, biometrics, information security, and other sectors. As of 2021, over 2.5 billion chips with XuanTie CPU architecture have been purchased and shipped.

Since T-Head has been introduced to the RISC-V community, it has successively developed XuanTie C910, C906, E906, E907, and E902 processors for different application fields. Except ++for XuanTie E907, all processors operate under an open-source license (https://github.com/T-head-Semi).

Overview of the XuanTie CPU Debug System

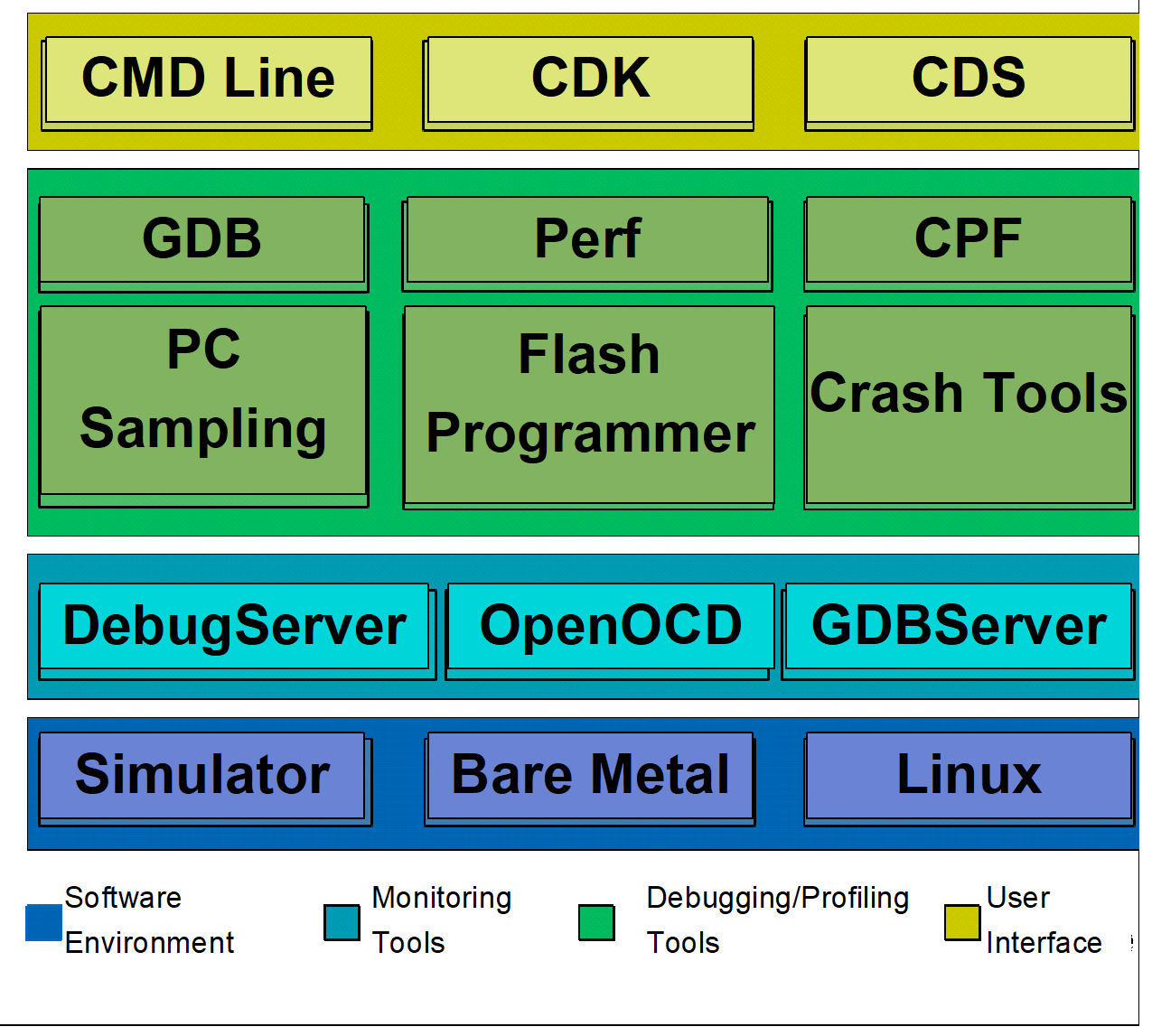

Figure 2.1 Overview of the XuanTie CPU debug system

As shown in Figure 2.1, the XuanTie CPU debug system consists of the following components:

- Software environment: The actual environment where the software runs. The environment is made up with simulators and commonly deployed hardware environments such as bare-metal and Linux kernel-based environments.

- Debugging and monitoring tools: Supporting tools that debug and control debugging programs. Such tools include the DebugServer, OpenOCD, and GDBServer. For the operating development boards, the system further requires cables and online simulation debugging tools,such as CKLink and JLink.

- Debugging and profiling tools: Typically used by developers for debugging inGDB, Perf, CPF, flash programmer, and crash tools.

- User interface (UI): The operational interface that users engage with. Such UIs include the command (CMD) line tools, Jianchi CDK and CDS. Most debugging and profiling tools can be presented as CMD lines. Compared with CMD line instruments, the Jianchi CDK and CDS offers a more friendly UI anda better development experience.

Debugging the XuanTie CPU with TRACE32®

As the world’s leading debugging tool, TRACE32® supports various debug features for processors with RISC-V architecture (https://www2.lauterbach.com/pdf/debugger_riscv.pdf). TRACE32® currently maintains the debugging and development of XuanTie E906, E907, and C906 processors (https://www.lauterbach.com/pro/pro__t-head.html).

Debugging features include:

- Program debugging in different stages (startup, bootloader, kernel, and application)

- Single-core and multi-core (AMP and SMP) debugging

- Assembly- and high-level language debugging

- Accessing registers

- Run/Stop

- Accessing memory

- Disassembly of the instruction sets extended by XuanTie

- Accessing CSRs extended by XuanTie

- Semihosting

The following two subsections describes the extended CSRs and instruction sets of XuanTie in TRACE32®.

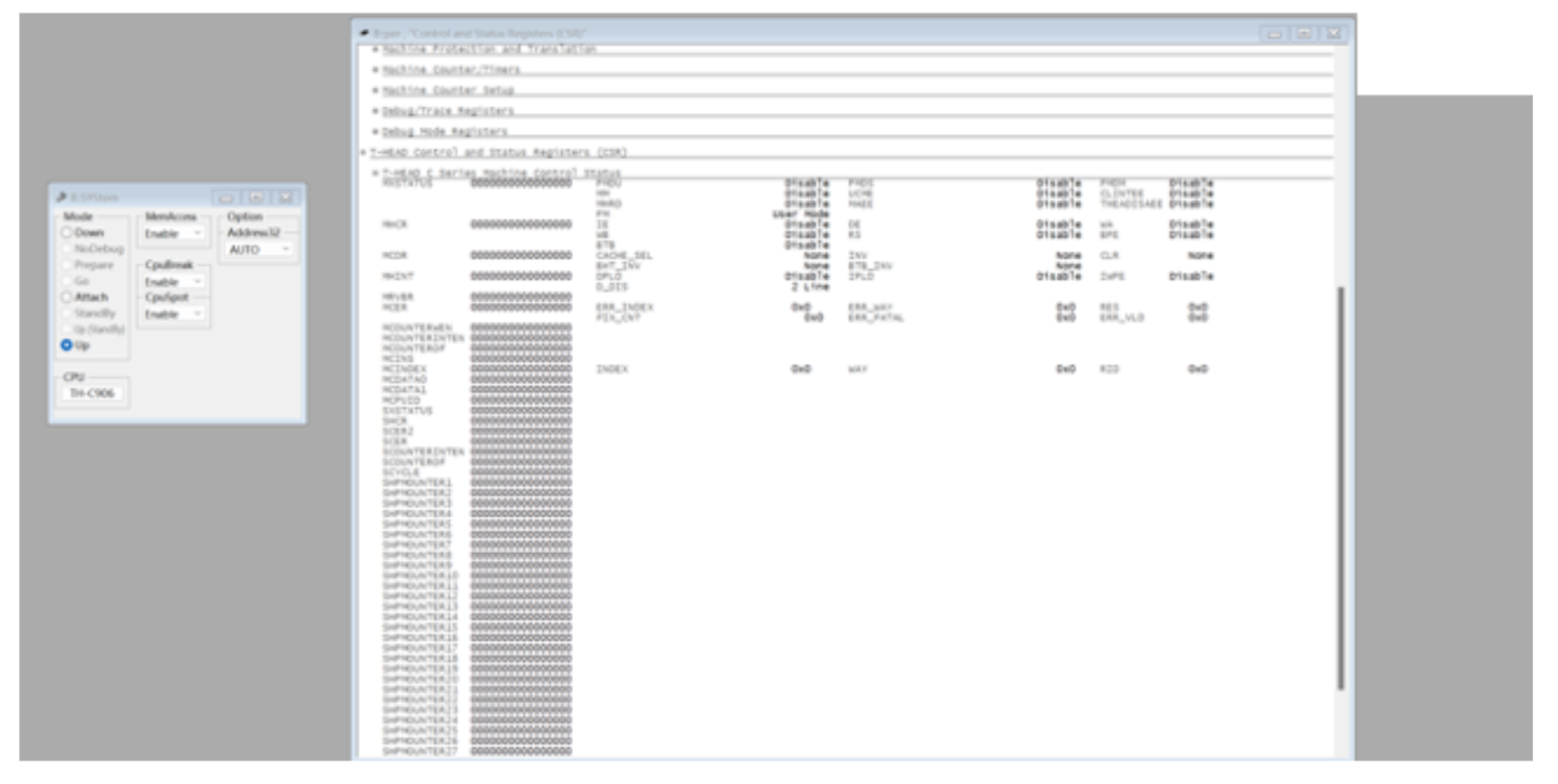

CSR from XuanTie

According to the XuanTie processor user manual, T-Head adds certain CSRs to XuanTie processors. TRACE32® supports the extended CSRs of the XuanTie processors. Developers need to view or modify these CSRs when using features.

Disassembling XuanTie Extensions ISA

T-Head adds many extended instructions to the functions and features of the XuanTie processor, for instance, LOAD/STORE with index, multiply-accumulate, cache management, and etc.. TRACE32® assists the disassembly of XuanTie extension instructions so that users can view the assembly instructions of the program during the debugging process.

TRACE32® supports the XuanTie processor to enrich the diversity of the RISC-V ecosystem. We look forward to further cooperation between T-Head and Lauterbach to deliver more debugging methods and functions to customers.