First RISC-V Foundation workshop outside North America sells out

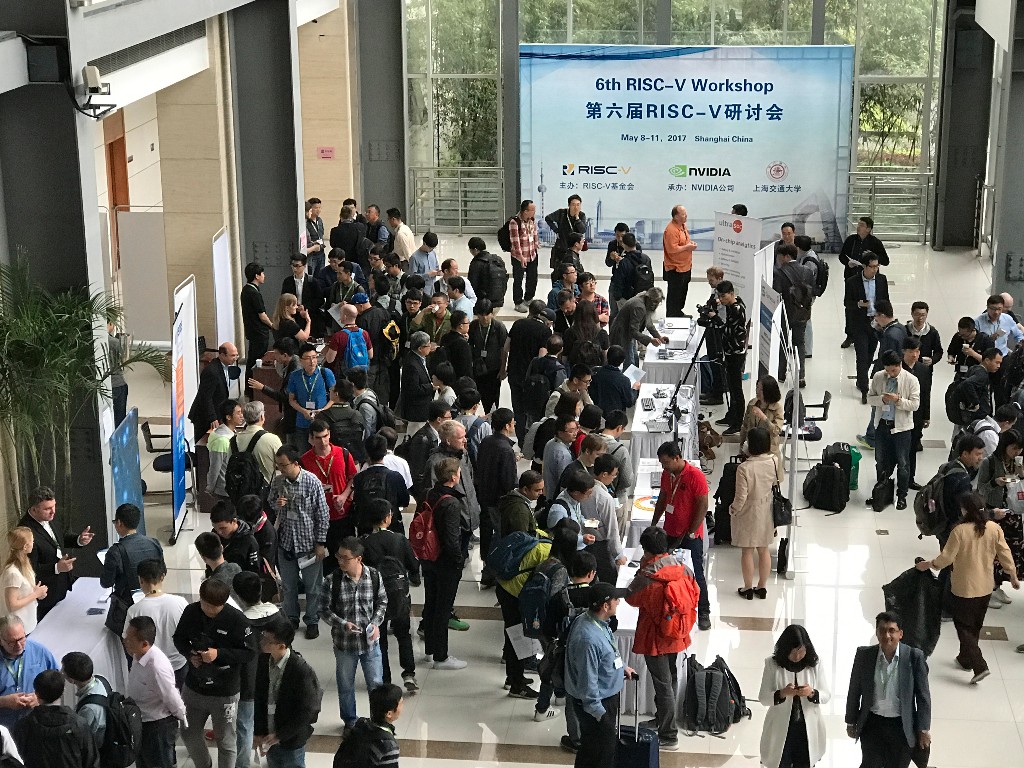

The 6th RISC-V Workshop, co-hosted by NVIDIA and the Shanghai Jiao Tong University (SJTU) was held in Shanghai China on May 8-11, 2017. This was our first RISC-V Foundation workshop held outside of North America and as with past workshops, this event was sold out with over 270 registered attendees. Workshop proceedings are available on the riscv.org site.

The 6th RISC-V Workshop, co-hosted by NVIDIA and the Shanghai Jiao Tong University (SJTU) was held in Shanghai China on May 8-11, 2017. This was our first RISC-V Foundation workshop held outside of North America and as with past workshops, this event was sold out with over 270 registered attendees. Workshop proceedings are available on the riscv.org site.

Maker Faire panel talks DiY chip making with RISC-V

Dave Patterson moderated a panel, entitled “Manufacturing Your Own Chips: Is Open Source (like RISC-V) Making it Easier?”, at Maker Faire Bay Area on May 20, 2017. Among the panelists were Ted Speers, board member, RISC-V foundation, Microsemi and Jack Kang (VP Product/BD, SiFive).

Dave Patterson moderated a panel, entitled “Manufacturing Your Own Chips: Is Open Source (like RISC-V) Making it Easier?”, at Maker Faire Bay Area on May 20, 2017. Among the panelists were Ted Speers, board member, RISC-V foundation, Microsemi and Jack Kang (VP Product/BD, SiFive).