There are now over a hundred RISC-V CPU cores listed in the RISC-V Exchange! Amazing. If you need a RISC-V CPU core, you’ll likely be able to find one that suits your needs… if you evaluate a hundred CPU cores to find it.

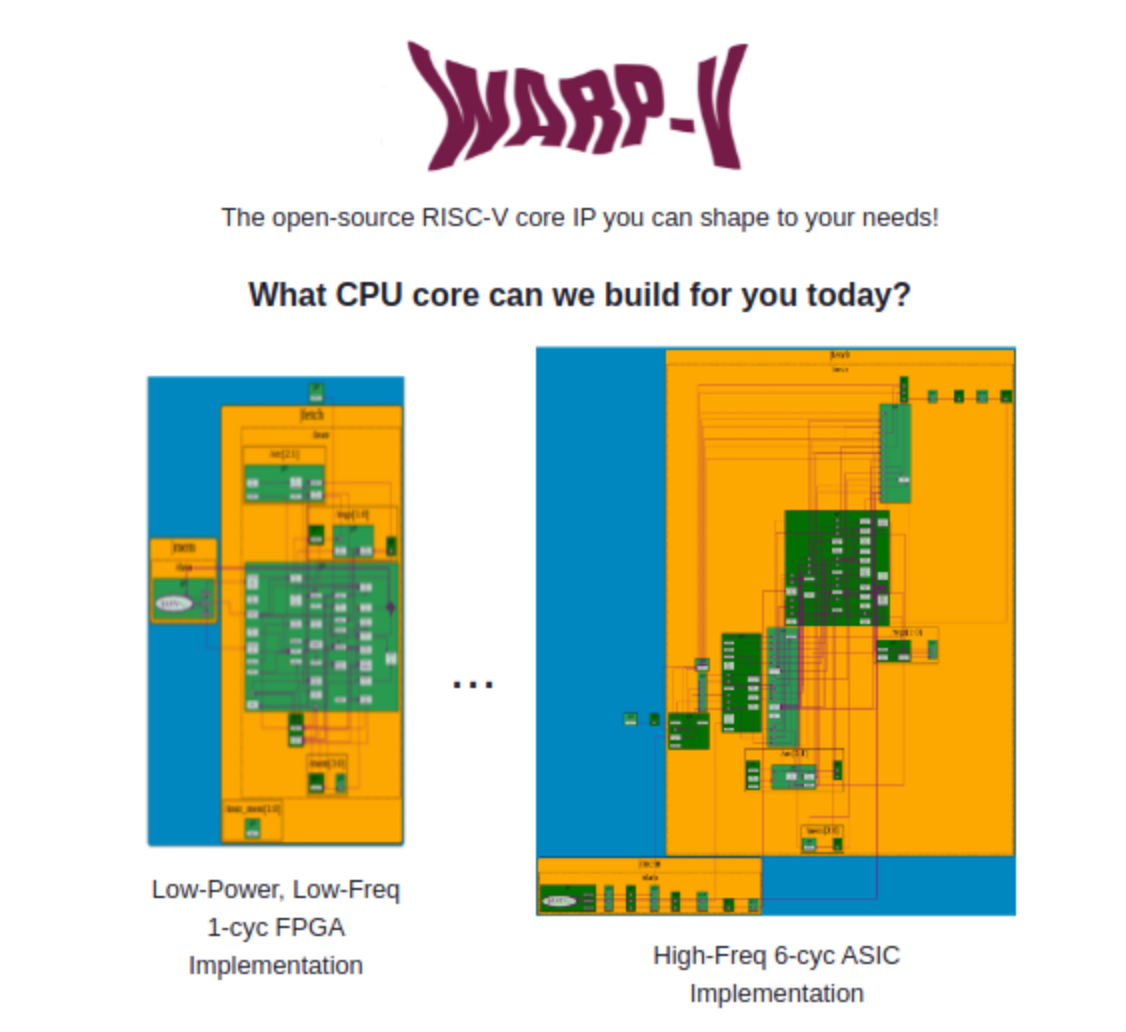

Or, now, you can configure exactly the core you need, and have it built in seconds, for free! WARP-V is the most flexible RISC-V CPU core available, and recently, Indiana University student, Adam Ratzman, created an online configurator for WARP-V. If you need a low-to-mid-range CPU core, check out Adam’s work at warp-v.org.

I spent most of my career designing high-end CPUs. I worked on CPUs that were more complex than we are likely to ever see again. CPUs went through this crazy cycle of escalating complexity in the race for single-core performance, followed later by the need to simplify.

Technology trends played a funny trick on us. In the nineties, as Moore’s Law gave us more silicon to play with, we gobbled it up to implement the next wiz-bang speculation trick to get a 1% edge in single-stream performance. But now tricks like that work against us in so many ways. They mean big cores, which mean longer wires with RC delays, which, in a modern process, dominate the cycle time and decrease performance. They mean more power, which we must trade-off for performance. They eat up space, which means fewer cores, which decreases performance. They increase design effort, which means it takes longer to optimize for the next process node, which hurts performance.

All this is to say that CPU design no longer requires 500-person design teams. I developed the initial WARP-V core in 2018 in a week and a half. It contains none of the advanced CPU microarchitectural techniques I’ve learned and developed throughout my career. And this might be exactly what you want. On the other hand, what is unique about WARP-V is that it is flexible. You’ll be able to optimize it for your own needs relatively quickly, and today, this is how we get performance.

The secret to WARP-V’s flexibility, and the focus of my startup, Redwood EDA, is Transaction-Level Verilog (TL-Verilog). TL-Verilog gives WARP-V its ability to provide, from the same source code, a single-cycle CPU, a seven-cycle CPU, or anywhere in between. It provides the ability to connect any configuration of WARP-V to a third-party RISC-V formal checker using the same single page of code. It helps to decouple the ISA from the microarchitecture, so WARP-V can support MIPS and other ISAs in addition to RISC-V. You just can’t get this flexibility from RTL, and this flexibility is the key to successful silicon.

WARP-V may not be everyone’s best option today. It has, thus far, been a small-scale effort, and is currently just the CPU core, not bundled with peripherals. But it should serve a good portion of the community quite well as it stands, and it shows a way forward to democratize CPUs without the need for a hundred different independent cores.

RISC-V has liberated the ISA. Now it’s time to liberate CPUs and other components. Save the patents for bigger things.