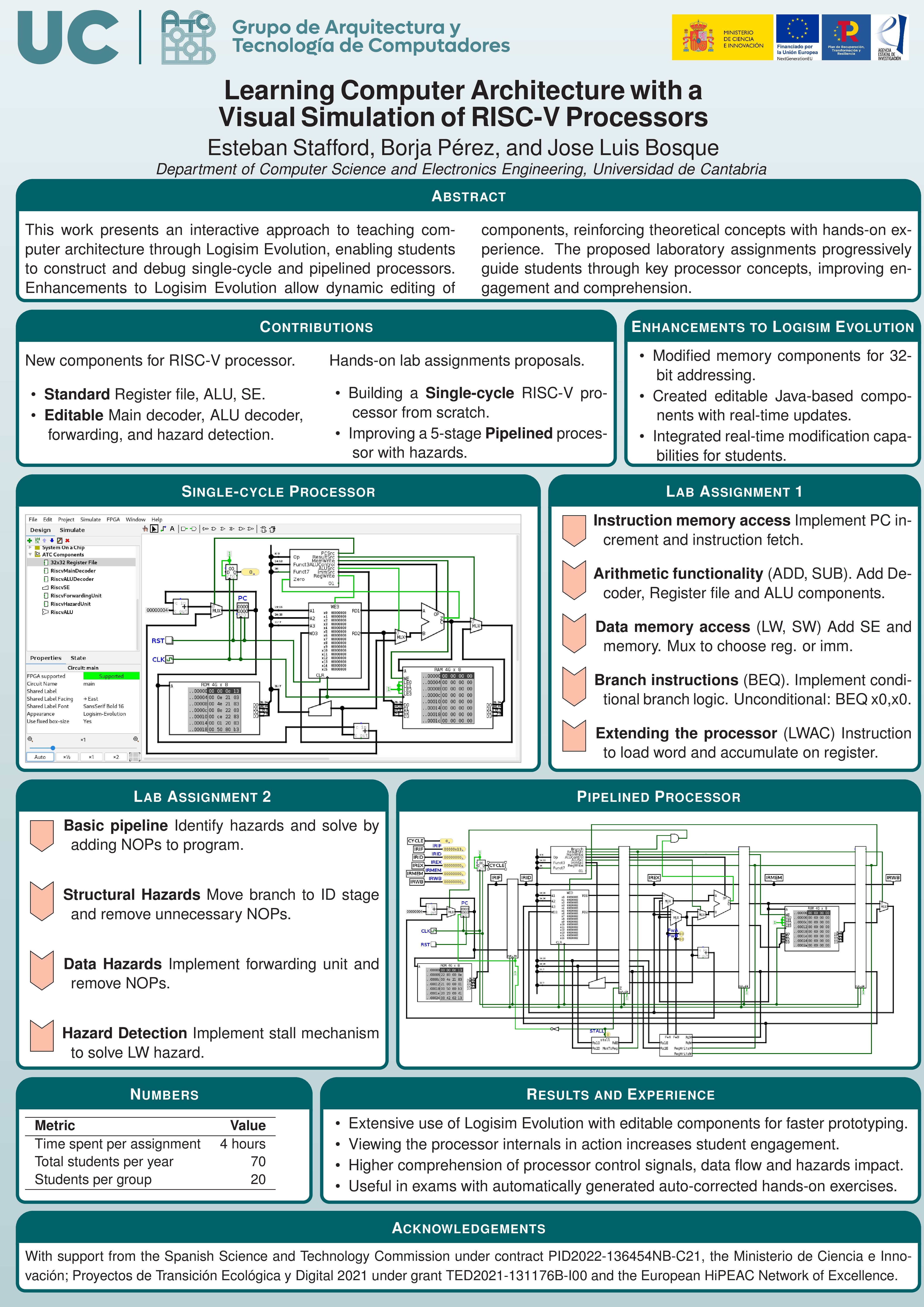

Project Snapshot

This work presents an interactive way of teaching computer architecture using Logisim Evolution, enabling students to construct and debug single-cycle and pipelined CPUs. Enhancements to Logisim Evolution allow dynamic editing of components, reinforcing theoretical concepts with hands-on experience. The proposed lab assignments progressively guide students through key processor concepts, improving engagement and comprehension.

In Their Own Words

Poster Preview

Meet the Authors

Esteban Stafford Fernández

Professor at Universidad de Cantabria in Spain

Esteban Stafford received his M.Sc. degree in Telecommunication Engineering from the University of Cantabria in 2001. After working for several years in IT companies in Germany, he returned to the University of Cantabria, where he served as a systems administrator, obtained his Ph.D. in Computer Science in 2015 and became part-time lecturer. He is currently a professor in the Department of Computer Engineering and Electronics at the University of Cantabria. He teaches courses on various computer science topics, including computer architecture, parallel programming and computer security. His research interests include computer architecture, parallel systems, workload scheduling and interconnection networks.

Borja Pérez Pavón

Professor at Universidad de Cantabria in Spain

Borja Pérez received his BSc degree in Computer Science and Engineering (2014) and his PhD in Science and Technology (2019) from Universidad de Cantabria. After finishing his PhD, he joined Barcelona Supercomputing Center as the lead of the performance modeling team of the Marenostrum Experimental Exascale Platform project. In 2023 Borja became an Assistant Professor in the Department of Computer Science and Engineering of Universidad de Cantabria. His research expertise spans memory hierarchy, heterogeneous systems, GPUs, and simulation technologies, and he has participated in several national and international projects, including collaborations with ARM and HUAWEI. Borja has also served as a member of the Steering and Program Committees for all three editions of the RISC-V Summit Europe and Program Chair of the 2025 edition.

Jose Luis Bosque Orero

Professor at Universidad de Cantabria in Spain

Dr. Jose Luis Bosque is a Full Professor in Computer Architecture and Technology at the Universidad de Cantabria (UC), where he also serves as Vice-chancellor of Digital Transformation and leads the Computer Architecture and Technology research group. With a PhD in Computer Engineering from UPM, his award-winning doctoral thesis focused on Heterogeneous Systems, a field he continues to lead as a principal investigator for the RISC-V Network in Spain and a founding member of the Spanish Open-Hardware Alliance. His extensive career includes over 40 national and international research projects, 15 industry contracts, and more than 120 scientific publications, alongside advising four PhD students and collaborating with international institutions like Trinity College Dublin and HLRS. Beyond research, he has dedicated over 6,000 hours to teaching across various universities, held significant academic leadership roles at UC, including Vice-Dean of Computer Engineering and Master’s coordinator, and contributed as an expert evaluator and Project Manager for the Agencia Estatal de Investigación.