RISC-V Summit 2021 – High Performance Processors, Other Interesting Talks | Michael Larabel, Phoronix

RISC-V Summit 2021 – High Performance Processors, Other Interesting Talks | Michael Larabel, PhoronixTaking place in San Francisco from Monday through yesterday evening was the RISC-V Summit for discussions around this dominant open-source processor ISA. For those that…

SCANDIANO, Italy, Dec. 9, 2021 — E4 Computer Engineering builds on 20+ years of developing and integrating innovative technologies and announces Monte Cimone, a cluster aimed…

SiFive Demonstrates RISC-V Rack Mount HPC Cluster | Anton Shilov, Tom’s Hardware

SiFive Demonstrates RISC-V Rack Mount HPC Cluster | Anton Shilov, Tom’s HardwareAs one of the main driving forces behind the RISC-V architecture, SiFive tends to introduce and showcase RISC-V solutions not available from anyone else in…

Two 64-bit RISC-V cores debut: StarFive Dubhe and CAS Nanhu | Eric Brown, LinuxGizmos

Two 64-bit RISC-V cores debut: StarFive Dubhe and CAS Nanhu | Eric Brown, LinuxGizmosStarFive has launched its 64-bit RISC-V “Dubhe” core with up to 2GHz @ 12nm performance plus Vector and Hypervisor extensions. Meanwhile, the Chinese Academy of…

SEGGER adds 64-bit RISC-V support to Embedded Studio | SEGGER

SEGGER adds 64-bit RISC-V support to Embedded Studio | SEGGERSEGGER's new release of Embedded Studio for RISC-V adds support for 64-bit RISC-V CPUs, including RV64I, RV64E and RV64GC with floating-point unit. It comes integrated with SEGGER emRun…

IAR Systems and Codasip collaborate on low-power RISC-V-based applications | Neil Tyler, New Electronics

IAR Systems and Codasip collaborate on low-power RISC-V-based applications | Neil Tyler, New ElectronicsIAR Systems and Codasip, a supplier of customisable RISC-V processor IP, are to work together to enable joint customers to build low-power embedded applications based…

With billions of chips in the market, RISC-V has seen widespread commercial adoption across industries and implementations, from embedded automotive to hyperscale AI, from 5G…

Vancouver based software studio Cartesian Theatre Corp. and SiFive, Inc., the founder and leader in RISC-V computing, are excited to announce CT’s Helios music recommendation…

Ventana will continue to contribute and accelerate technical progress and market adoption of RISC-V ZURICH – Dec. 6, 2021 – RISC-V International, a global open hardware…

SiFive’s new chip could lead to revamped phone brains in 2023 | Stephen Shankland, CNET

SiFive’s new chip could lead to revamped phone brains in 2023 | Stephen Shankland, CNETThe Performance P650, a RISC-V processor family member, is 50% faster than its predecessor but slower than top-end chips in Samsung and Apple smartphones. A…

HPMicro Semiconductor Announces the Release of the HPM6000 Series of Microcontrollers with AndesCore™ Dual D45 Cores | Andes Technology

HPMicro Semiconductor Announces the Release of the HPM6000 Series of Microcontrollers with AndesCore™ Dual D45 Cores | Andes TechnologyCurrently, the HPM6000 series is the world’s most powerful real-time RISC-V microcontrollers, with a clock speed up to 800 MHz, setting a new performance record…

SiFive Raises RISC-V performance bar with New Best-in-Class SiFive Performance P650 Processor | SiFive

SiFive Raises RISC-V performance bar with New Best-in-Class SiFive Performance P650 Processor | SiFiveThe SiFive Performance P650 processor is expected to be the fastest licensable RISC-V processor IP core in the market, bringing RISC-V into new markets and…

Imperas Expands Partnership with Valtrix to Address Growing RISC-V Verification Market

Imperas Expands Partnership with Valtrix to Address Growing RISC-V Verification MarketImperas Software Ltd., the leader in RISC-V processor verification technology, today announced a multi-year distribution and support agreement with Valtrix Systems, provider of design verification products…

Video: SSRC Collaborates with Global Universities on RISC-V-Based Secure Flight Computer System | ATRC

Video: SSRC Collaborates with Global Universities on RISC-V-Based Secure Flight Computer System | ATRCTII’s Secure Systems Research Centre (SSRC) has partnered with global universities to develop a RISC-V-Based Secure Flight Computer System. SSRC is a strategic member of…

SiFive Deepens RISC-V Core Lineup | William G. Wong, Electronic Design

SiFive Deepens RISC-V Core Lineup | William G. Wong, Electronic DesignSiFive keeps cranking out new versions of its RISC-V cores. Its two most recent additions include the Performance P550 core and the Performance P270 vector…

BSC, Codeplay and SiFive help accelerate applications on RISC-V thanks to V-extension support in LLVM

BSC, Codeplay and SiFive help accelerate applications on RISC-V thanks to V-extension support in LLVMThe Barcelona Supercomputing Center (BSC) has been collaborating with Codeplay Software and SiFive to implement support for the RISC-V V-extension v0.10 in the LLVM compilation infrastructure.…

InCore and Tessolve announce the availability of our open source RISC-V Core Verification tool - RiVer Core. RiVer Core is a python based extensible and…

Stefano Di Mascio, Alessandra Menicucci, Eberhard Gill, Gianluca Furano and Claudio Monteleone Abstract The use of deep neural networks (DNNs) in terrestrial applications went from niche…

Canonical Launches Its First Official Ubuntu RISC-V Builds, for SiFive’s Unleashed and Unmatched | Gareth Halfacree, hackster.io

Canonical Launches Its First Official Ubuntu RISC-V Builds, for SiFive’s Unleashed and Unmatched | Gareth Halfacree, hackster.ioPartnership with SiFive aims to make Ubuntu the "reference OS for early adopters" of Linux on desktop-class RISC-V. Canonical has confirmed official RISC-V support for…

Canonical Announces Ubuntu Support For RISC-V | Steven Dickens, Futurum

Canonical Announces Ubuntu Support For RISC-V | Steven Dickens, FuturumCanonical announces Ubuntu operating system support for a new architecture, namely RISC-V. Working with RISC-V core IP designer and development board manufacturer, SiFive, Canonical announced…

TII’s Secure Systems Research Centre Collaborates with Global Universities on RISC-V-Based Secure Flight Computer System

TII’s Secure Systems Research Centre Collaborates with Global Universities on RISC-V-Based Secure Flight Computer SystemTechnology Innovation Institute (TII), the applied research pillar of Abu Dhabi’s Advanced Technology Research Council (ATRC), today announced that its Secure Systems Research Centre (SSRC)…

In this video we explore getting Ubuntu installed on the HiFive Unmatched. Then we have a little fun with some benchmarks, followed up by trying…

SiFive Collaborates with Imperas on Models of SiFive’s RISC-V Core IP Portfolio

SiFive Collaborates with Imperas on Models of SiFive’s RISC-V Core IP PortfolioImperas Software Ltd.,the leader in virtual platforms and high-performance software simulation, today announced that SiFive, Inc., the industry leader in RISC-V processors and silicon solutions, has…

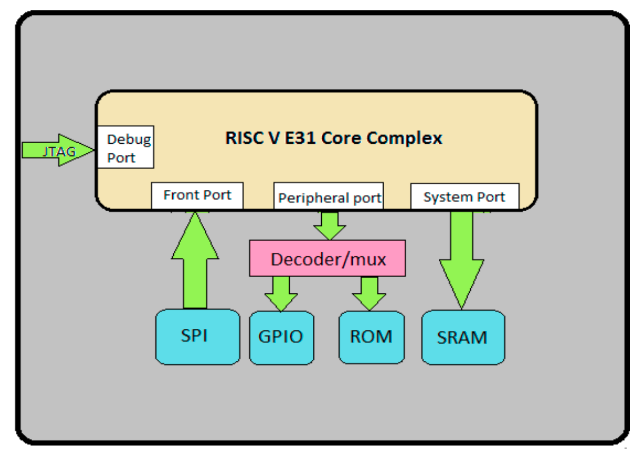

Automotive Hardware Functional Safety (FuSa) Features: ISO 26262

Automotive Hardware Functional Safety (FuSa) Features: ISO 26262In all critical applications like aircrafts, medical equipment and automobiles, there is a requirement for the systems to be reliable and safe. These requirements are…