How the RISC-V Atomic Extension Gives You Superior Bit Manipulation Capabilities | Bill Giovino, Digi-Key

How the RISC-V Atomic Extension Gives You Superior Bit Manipulation Capabilities | Bill Giovino, Digi-KeyThe rate of RISC-V architecture adoption is quickly snowballing, and for good reason, its influence in the industry is increasing. Besides the core architecture and…

Codasip Appoints Brett Cline to Drive Company Growth Worldwide | Codasip

Codasip Appoints Brett Cline to Drive Company Growth Worldwide | CodasipCodasip, the leading supplier of customizable RISC-V processor IP, today announced the company has made a senior appointment to boost its global sales effort, with…

What Computing Tech Will Drive Future Space Exploration? | Michelle Hampson, IEEE Spectrum

What Computing Tech Will Drive Future Space Exploration? | Michelle Hampson, IEEE SpectrumAt the heart of every successful space mission is a sophisticated and capable computer system. In the 1960s, relatively basic computing systems took humankind to…

Abstract: Supporting masking countermeasures for non-invasive side-channel security in instructions set architectures is a hard problem. Masked operations often have a large number of inputs…

How the Imagination RVfpga: Understanding Computer Architecture course is giving engineering under-grads real-world skills | Robert Owen, Imagination Technologies

How the Imagination RVfpga: Understanding Computer Architecture course is giving engineering under-grads real-world skills | Robert Owen, Imagination TechnologiesIf you were to take a look through the academic materials now available about RISC-V you will find a wealth of information around SoC creation,…

Looking Towards the Future: FreeBSD on the RISC-V Architecture | Klara

Looking Towards the Future: FreeBSD on the RISC-V Architecture | KlaraThe majority of people in the tech community are well aware of the two main chip architectures: x86 and ARM. Each has its own strengths…

With Pixel 6 and Pixel 6 Pro, we’re launching our most secure Pixel phone yet, with 5 years of security updates and the most layers…

RISC-V-Based VEGA Brings Continual Learning to TinyML with an Order of Magnitude Efficiency Gain | Gareth Halfacree, Hackster.io

RISC-V-Based VEGA Brings Continual Learning to TinyML with an Order of Magnitude Efficiency Gain | Gareth Halfacree, Hackster.ioA team of computer scientists have developed a RISC-V-based platform for embedded machine learning workloads — and say it offers 65 times the performance and…

High-Level Synthesis For RISC-V | Brian Bailey, Semiconductor Engineering

High-Level Synthesis For RISC-V | Brian Bailey, Semiconductor EngineeringAbstraction is the key to custom processor design and verification, but defining the right language and tool flow is a work in progress. High-quality RISC-V…

Kneron Edge AI SoC Powered by Andes RISC-V Processor Core D25F | Andes Technology

Kneron Edge AI SoC Powered by Andes RISC-V Processor Core D25F | Andes TechnologyKneron Inc., the San Diego-based Edge AI solution provider, together with Andes Technology Corporation (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099), a leading supplier of high-performance,…

Open source toolchains are key to building collaborative ecosystems, welcoming to new approaches, opportunistic/focused innovations and niche use cases. The ASIC design domain, especially in…

With the high performance Alibaba T-Head XuanTie processor coming to market, we believe it will benefit the RISC-V industry to port RISCV to the Android…

Alibaba Future-Proofing Cloud OS, Will Support Multiple Architectures | WebProNews, Matt Milano

Alibaba Future-Proofing Cloud OS, Will Support Multiple Architectures | WebProNews, Matt MilanoAlibaba is working to make its Apsara cloud OS compatible with a variety of architectures in an effort to future-proof it. Alibaba started as an…

Recently, Huawei released their first RISC-V development system to help engineers use the HarmonyOS operating system targeted at IoT devices. So why is Huawei looking…

TII becomes a strategic member of the global organisation whose open-source standard allows for collaboration and breakthroughs in the computer chip industry, including the ability…

PUFsecurity and Andes Technology Cooperate to Integrate Crypto Coprocessor PUFiot into RISC-V AIoT Security Platform

PUFsecurity and Andes Technology Cooperate to Integrate Crypto Coprocessor PUFiot into RISC-V AIoT Security PlatformHsinchu Taiwan, June 02, 2021 (GLOBE NEWSWIRE) -- PUFsecurity, a security solutions IP company, and Andes Technology (TWSE: 6533), a leading RISC-V CPU IP vendor,…

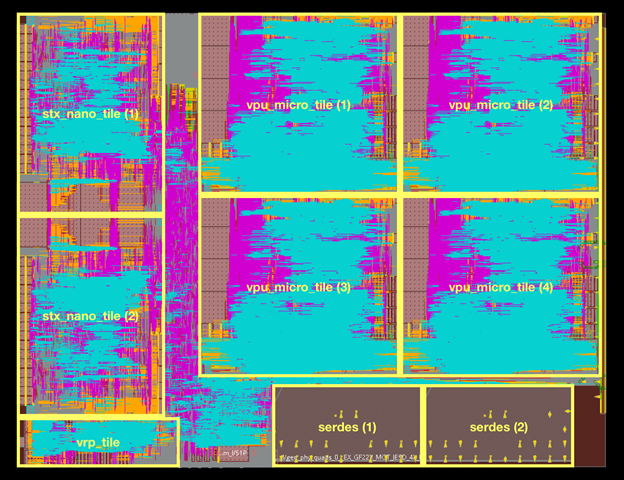

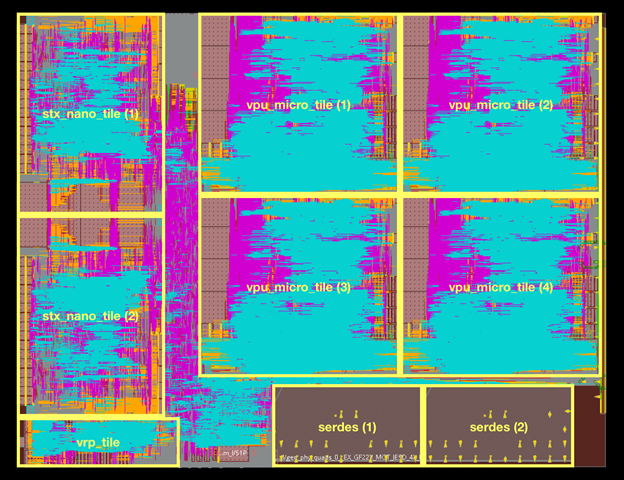

European supercomputer test chip tapes out | eeNews, Peter Clarke

European supercomputer test chip tapes out | eeNews, Peter ClarkeThe EPAC 1.0 test chip is now ready to be sent to fabrication, It contains a number of accelerator cores some based on RISC-V instruction…

#TII’s Secure Systems Research Centre (#SSRC) has become a strategic member of RISC-V International, an organisation which directs the future development and drives the adoption…

ABU DHABI, (UrduPoint / Pakistan Point News / WAM - 02nd Jun, 2021) Technology Innovation Institute (TII), the applied research pillar of Abu Dhabi’s Advanced…

Connecting to the ISS crew manifest using an online API, the BBC HiFive and its onboard ESP32 using Micropython.

Experts at the Table: This is the last part of the series of articles derived from the DVCon panel that discussed Verification in the Era of…

June 1, 2021 -- The European Processor Initiative (EPI) https://www.european-processor-initiative.eu/, a project with 28 partners from 10 European countries, with the goal of helping the EU achieve…

European Processor Initiative Announces EPAC1.0 RISC-V Test Chip Taped-out | HPCWire

European Processor Initiative Announces EPAC1.0 RISC-V Test Chip Taped-out | HPCWireJune 1, 2021 — The European Processor Initiative (EPI), a project with 28 partners from 10 European countries, with the goal of helping the EU…

*RISC-V 32-bit Instruction Type Decode logic design in 120sec* Just imagine what all things you can do in RISC-V MYTH 5-day workshop. Many participants have…