Google Summer of Code’21 at FOSSi Foundation: TensorCore Extension for Deep Learning | Nitin Mishra

Google Summer of Code’21 at FOSSi Foundation: TensorCore Extension for Deep Learning | Nitin MishraIntroduction This has been a great summer! I was fortunate enough to be accepted into the Google Summer Code(GSOC) program for the “TensorCore Extension for…

Accelerating exhaustive and complete verification of RISC-V processors | Ashish Darbari, Axiomise

Accelerating exhaustive and complete verification of RISC-V processors | Ashish Darbari, AxiomiseAs processor architecture and design development becomes completely liberated with open-source RISC-V instruction set architecture (ISA), the race to get RISC-V silicon in our hands…

Listen to the full episode of Soft Robotics Podcast.

Andes Technology and Cyberon Collaborate to Provide Edge-Computing Voice Recognition Solution on DSP-capable RISC-V Processors | Chip Estimate

Andes Technology and Cyberon Collaborate to Provide Edge-Computing Voice Recognition Solution on DSP-capable RISC-V Processors | Chip EstimateCyberon Corporation, a leading embedded speech solution provider, and Andes Technology (TWSE: 6533), a major supplier for high efficiency, low-power 32/64-bit RISC-V processor cores, announced…

Imagination Technologies to design RISC-V cores | Jean-Luc Aufranc, CNX Software

Imagination Technologies to design RISC-V cores | Jean-Luc Aufranc, CNX SoftwareNow better known for its PowerVR embedded GPUs, Imagination Technologies tried to enter the CPU market by purchasing MIPS Technologies and introducing microAptiv, interAptiv, and…

A Hardware Platform for Ensuring OS Kernel Integrity on RISC-V

A Hardware Platform for Ensuring OS Kernel Integrity on RISC-VThe OS kernel is typically preassumed as a trusted computing base in most computing systems. However, it also implies that once an attacker takes control…

As we continue our push for more software-driven hardware development as part of our work within CHIPS Alliance and RISC-V, we see an increasing need…

Esperanto Emerges From Stealth With 1,000-Core RISC-V AI Accelerator | Sally Ward-Foxton, EE Times

Esperanto Emerges From Stealth With 1,000-Core RISC-V AI Accelerator | Sally Ward-Foxton, EE TimesCoinciding with the Hot Chips conference, startup Esperanto emerged from stealth mode this week with the highest performance commercial RISC-V chip to date – a…

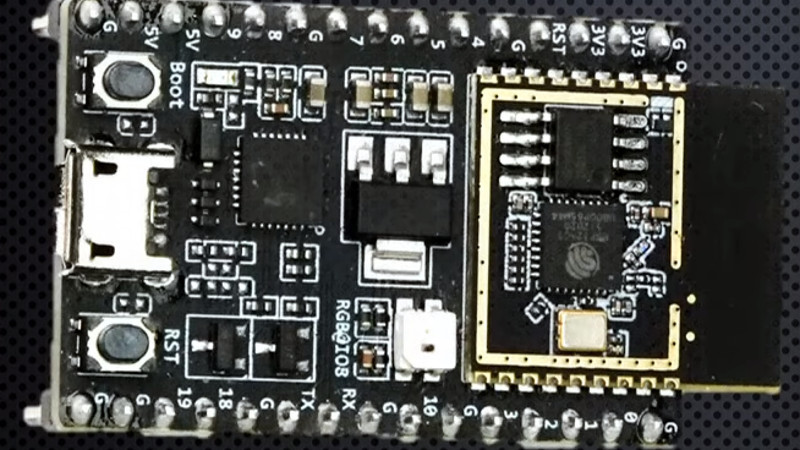

French: Espressif dévoile une puce-système radio ESP32 à cœur RISC-V… compatible Bluetooth, Zigbee et Thread | Pierrick Arlot, L’Embarqué

French: Espressif dévoile une puce-système radio ESP32 à cœur RISC-V… compatible Bluetooth, Zigbee et Thread | Pierrick Arlot, L’EmbarquéConnu pour ses puces-systèmes compatibles Wi-Fi, Bluetooth et Bluetooth Low Energy ESP32, Espressif Systems semble avoir été définitivement séduit par l’architecture de processeur RISC-V. Après…

Rowhammer is a hardware vulnerability that affects DRAM memory chips and can be exploited to modify memory contents, potentially providing root access to the system. It…

Imagination Technologies Enters the CPU Space With RISC-V Architecture | Francisco Pires, Tom’s Hardware

Imagination Technologies Enters the CPU Space With RISC-V Architecture | Francisco Pires, Tom’s HardwareImagination Technologies today announced (via Design & Reuse) its financial results for the first half of 2021, which show the company is poised for a…

For close to 30 years, SUSE has excelled at helping businesses choose an Open path. From the industry’s most adaptable Enterprise Linux to a leading…

In den letzten Folgen war vom Raspberry Pi Pico die Rede. Bevor sich das Blog weiterhin dem Pico widmet, adressiert dieses Extra-Posting den neuen Microcontroller…

UPPSALA, Sweden, March 4, 2021 /PRNewswire/ -- IAR Systems®, the future-proof supplier of software tools and services for embedded development, announces the availability of a certified edition of…

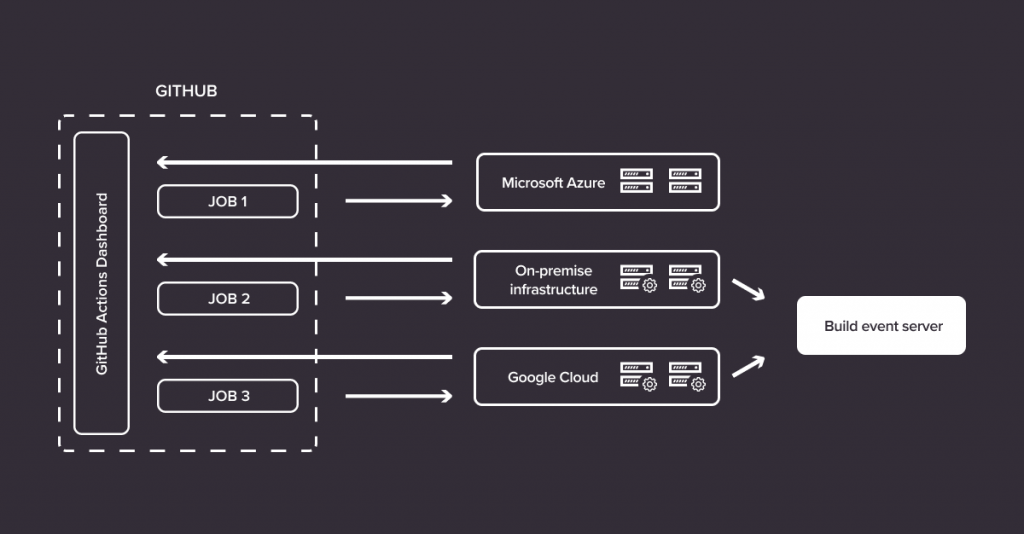

GitHub Actions self-hosted runners, Build Event Server and Google Cloud | Antmicro

GitHub Actions self-hosted runners, Build Event Server and Google Cloud | AntmicroContinuous Integration and smart lifecycle management are key for high-tech product development, which is often a complex and multi-faceted process that requires automation to be…

Free Courses Now Available to Learn ‘RISC-V’ by The Linux Foundation & RISC-V International | Sourav Rudra, It’s Foss News

Free Courses Now Available to Learn ‘RISC-V’ by The Linux Foundation & RISC-V International | Sourav Rudra, It’s Foss NewsThe Linux Foundation is the official organization behind Linux and is at the forefront for collaboration on open-source software, open hardware, open data and open standards.…

RISC-V Fast Tracks Simpler Extensions | eeJournal, Jim Turley

RISC-V Fast Tracks Simpler Extensions | eeJournal, Jim TurleyOne of the charming aspects of RISC-V is that it’s so… flexible. As an open-source processor specification, absolutely anyone can use it, modify it, and…

RISC-V, the emerging open-source instruction set processor architecture, is growing up. Sure, most of the attention has come from hardware hackers playing on RISC-V processors…

Lattice Expands mVision Solutions Stack Capabilities | businesswire

Lattice Expands mVision Solutions Stack Capabilities | businesswireHILLSBORO, Ore.--(BUSINESS WIRE)--Lattice Semiconductor Corporation (NASDAQ: LSCC), the low power programmable leader, launched the latest version of its award-winning solutions stack for low power embedded vision…

Imperas Donates Latest RV32/64K Crypto (scalar) Architectural Validation Test Suites to the RISC-V Verification Ecosystem | imperas

Imperas Donates Latest RV32/64K Crypto (scalar) Architectural Validation Test Suites to the RISC-V Verification Ecosystem | imperasOxford, UK – March 1st, 2021 – Imperas Software Ltd., the leader in RISC-V processor verification technology, today announced the release of the latest update to the…

RISC-V Is On a Roll. Is It Ready to Take a Seat Alongside Intel, AMD, and Arm? | Data Center Knowledge, Christine Hall

RISC-V Is On a Roll. Is It Ready to Take a Seat Alongside Intel, AMD, and Arm? | Data Center Knowledge, Christine HallRISC-V, the emerging open source instruction set architecture for processors that have so far been used mostly as accelerators, is suddenly on a roll and appears about ready…

EXPLORING THE OPEN SOURCE THAT REALLY GOES INTO A RISC-V CHIP | Hackaday, Jenny List

EXPLORING THE OPEN SOURCE THAT REALLY GOES INTO A RISC-V CHIP | Hackaday, Jenny ListIt’s an exciting time in the world of microprocessors, as the long-held promise of devices with open-source RISC-V cores is coming to fruition. Finally we…

WHAT IS CODAL? | Codasip

WHAT IS CODAL? | CodasipCodAL, standing for Codasip Architectural Language, is central to developing a processor core using Codasip Studio. The language has a C-like syntax and it merges good practices…