Ultra-Low-Power RISC-V System-on-Chip features Adaptive Body Biasing Technology | Abhishek Jadhav, CNX Software

Ultra-Low-Power RISC-V System-on-Chip features Adaptive Body Biasing Technology | Abhishek Jadhav, CNX SoftwareCSEM and USJC together have developed an ultra-low-power RISC-V chip for electronic gadgets such as wearables. The semiconductor companies, from Switzerland and Japan respectively, have…

EdgeQ Samples 5G Basestation-on-a-Chip | Sally Ward-Foxton, EE Times

EdgeQ Samples 5G Basestation-on-a-Chip | Sally Ward-Foxton, EE TimesEdgeQ, the startup making basestation-on-a-chip silicon and software for 5G deployments, is now sampling its chip and phy software. The company has also released a…

ChaCha is a high-throughput stream cipher designed with the aim of ensuring high-security margins while achieving high performance on software platforms. RISC-V, an emerging, free,…

DIY LED Cube For The Masses | Inderpreet Singh, Hackaday

DIY LED Cube For The Masses | Inderpreet Singh, HackadayNo matter what the size or shape of an LED, it brings out the curiosity in every hardware nerd, and is the lifeblood of badge…

What does it look like to program with no operating system? Can we have direct access to hardware using a high-level language like C++? How…

EdgeQ samples SoC for 5G and AI inference engines | Michael Vizard, Venture Beat

EdgeQ samples SoC for 5G and AI inference engines | Michael Vizard, Venture BeatEdgeQ revealed today it has begun sampling a 5G base station-on-a-chip that allows AI inference engines to run at the network edge. The goal is…

This article describes the first public implementation and evaluation of the latest version of the RISC-V hypervisor extension (H-extension v0.6.1) specification in a Rocket chip…

RISC-V Chip Delivers Quantum-Resistant Encryption | Charles Q. Choi, IEEE Spectrum

RISC-V Chip Delivers Quantum-Resistant Encryption | Charles Q. Choi, IEEE SpectrumMany new encryption techniques seek to resist powerful attacks that could be done using future quantum computers, but these methods often require enormous processing power.…

Working With RISC-V | Ed Sperling, Semiconductor Engineering

Working With RISC-V | Ed Sperling, Semiconductor EngineeringRISC-V is coming on strong, but working with this open-source processor core isn’t as simple as plugging in a commercial piece of IP. Zdenek Prikryl,…

RISC-V Wireless Chip With Adaptive Body Bias Reaches pW power | Nick Flaherty, EE News Europe

RISC-V Wireless Chip With Adaptive Body Bias Reaches pW power | Nick Flaherty, EE News EuropeResearchers in Switzerland and Japan have developed a RISC-V wireless system on chip with anactive power consumption as low as 10µA and an ultra low…

RISC-V RV32I R-Type | Maven Silicon

RISC-V RV32I R-Type | Maven SiliconThis video explains the RV32I R-Type instructions. RISC-V is growing rapidly, follow this RISC-V video blog series to obtain knowledge about RISC-V processors, Instruction formats,…

Side-channel analysis (SCA) attacks pose a major threat to embedded systems due to their ease of accessibility. Realising SCA resilient cryptographic algorithms on embedded systems…

Tianyihexin Licenses Codasip L30 for Powering Intelligent Wearable Device Solutions | Codasip

Tianyihexin Licenses Codasip L30 for Powering Intelligent Wearable Device Solutions | CodasipMunich, Germany – February 24th, 2021 – Codasip, the leading supplier of customizable RISC-V® embedded processor IP, announced today that Nanjing Tianyihexin Electronics, an innovative…

Imagination’s GPU selected for Beagle V RISC-V AI single board computer | Neil Tyler, New Electronics

Imagination’s GPU selected for Beagle V RISC-V AI single board computer | Neil Tyler, New ElectronicsStarFive, a provider of RISC-V processors, platforms and solutions, has licensed Imagination's IMG B-Series graphics processing unit (GPU) IP to support the development of its…

RISC-V International Unveils Fast Track Architecture Extension Process and Ratifies ZiHintPause Extension | Design & Resuse

RISC-V International Unveils Fast Track Architecture Extension Process and Ratifies ZiHintPause Extension | Design & ResuseFast Track significantly accelerates the ratification of small architecture extensions Read the full article.

Presented by Pete Alexander, John Holden, Harry Cooper, Byron Theobald, Aaryaman Bhattacharya, Matthew Johns, University of Southampton

Smart public transportation system using VEGA Processor [ RISC-V ISA] | VEGA Processors

Smart public transportation system using VEGA Processor [ RISC-V ISA] | VEGA ProcessorsDemonstrating Smart public transportation system using VEGA Microprocessor based on RISC-V ISA

LeaRnV: a RISC-V based Embedded System Design Framework for Education and Research Development | TIMA Laboratory

LeaRnV: a RISC-V based Embedded System Design Framework for Education and Research Development | TIMA LaboratoryDesigning a modern System on a Chip is based on the joint design of hardware and software (co-design). However, understanding the tight relationship between hardware…

Using gem5 and RISC-V simulation to enable the optimization of heterogeneous architectures | HiPEAC

Using gem5 and RISC-V simulation to enable the optimization of heterogeneous architectures | HiPEACThis tutorial will provide an introduction to architectural simulation using the gem5-X simulation framework (which is an extended and improved version of the gem5 simulator)…

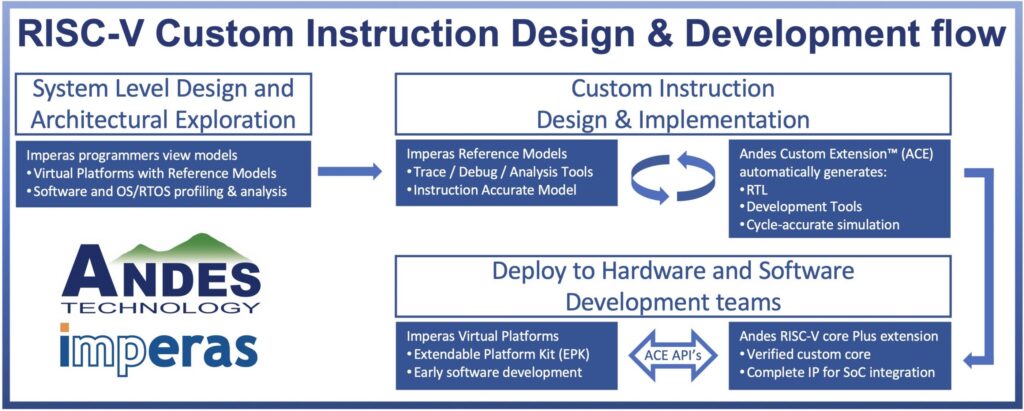

Webinar: RISC-V Custom Instructions – Design, Development and Deployment, Feb 24 2021 | Imperas

Webinar: RISC-V Custom Instructions – Design, Development and Deployment, Feb 24 2021 | ImperasImperas Software Ltd., the leader in RISC-V processor verification technology, today announced a joint webinar with Andes on optimizing RISC-V cores with custom extensions for…

Pine64 introduces Quartz64 single-board PC with RK3566 processor, teases upcoming RISC-V board | Brad Linder, Liliputing

Pine64 introduces Quartz64 single-board PC with RK3566 processor, teases upcoming RISC-V board | Brad Linder, LiliputingOne of the next single-board computers from Pine64 is a 5.2″ x 3.1″ mini PC powered by a 1.8 GHz Rockchip RK3566 ARM Cortex-A55 processor…

RISC-V: How much is open source? Featuring the new ESP32-C3 | Andreas Spiess

RISC-V: How much is open source? Featuring the new ESP32-C3 | Andreas SpiessWhen I got these new RISC-V ESP32 boards in my mail, I asked myself: Is this new technology revolutionary as written everywhere? What are the…