The world's most powerful RISC-V development platform is here, and we are building a computer with it! This is a first look at SiFive's new…

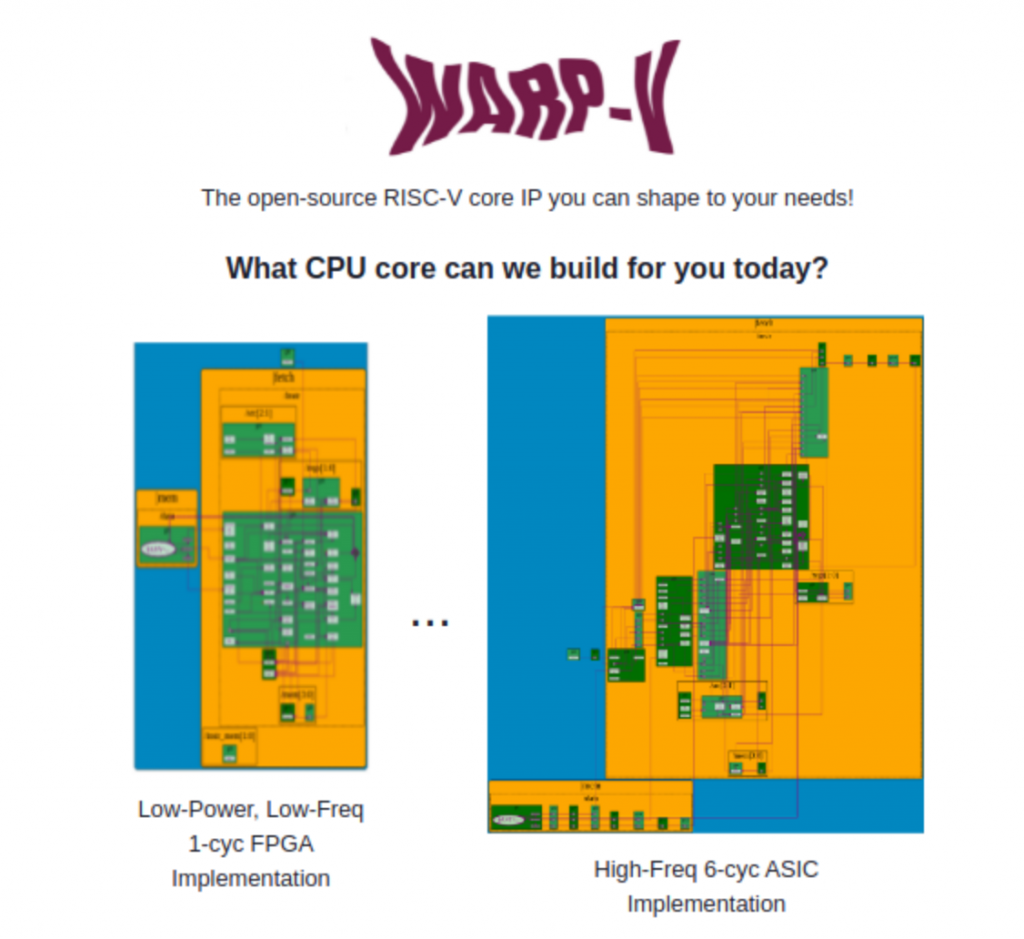

A Free RISC-V CPU Core Builder – Democratizing CPUs | Steve Hoover, Redwood EDA

A Free RISC-V CPU Core Builder – Democratizing CPUs | Steve Hoover, Redwood EDAThere are now over a hundred RISC-V CPU cores listed in the RISC-V Exchange! Amazing. If you need a RISC-V CPU core, you’ll likely be…

NSITEXE achieves world’s first RISC-V processor with vector extension certified for ISO 26262 ASIL D ready product |

NSITEXE achieves world’s first RISC-V processor with vector extension certified for ISO 26262 ASIL D ready product |The DR1000C, a data flow processor (DFP) developed by NSITEXE, Inc. (headquartered in Minato Ward, Tokyo, Japan; President and CEO: Yukihide Niimi; hereinafter “NSITEXE”) has…

RISC-V RV32I Assembly – Multiplication | Maven Silicon

RISC-V RV32I Assembly – Multiplication | Maven SiliconThis video shows how we can implement the Multiplication using add and shift RV32I instructions. RISC-V is growing rapidly, follow this RISC-V video blog series…

Chinese Wearable Technology Firm Huami to Launch New OS with Better Understanding of Users | Pandaily

Chinese Wearable Technology Firm Huami to Launch New OS with Better Understanding of Users | PandailyChinese smart wearable device manufacturer Zepp Health, previously known in the international market as Huami, has announced that it planned to unveil its own OS,…

Andes certifies Imperas RISC-V Reference Models for the new RISC-V P (SIMD/DSP) extension

Andes certifies Imperas RISC-V Reference Models for the new RISC-V P (SIMD/DSP) extensionImperas Software Ltd., the leader in virtual platforms and high-performance software simulation, today announced that Andes Technology Corp., a leading supplier of performance-efficient and extensible 32/64-bit…

NodeMCU Launches Sub-$5 Espressif ESP32-C3 RISC-V Development Boards | Gareth Halfacree, Hackster.io

NodeMCU Launches Sub-$5 Espressif ESP32-C3 RISC-V Development Boards | Gareth Halfacree, Hackster.ioThe first commercial development boards featuring Espressif's RISC-V-based ESP32-C3, a drop-in replacement for the popular ESP8266, have appeared on the market — costing as little…

This is part of a series on the blog where we explore RISC-V by breaking down real programs and explaining how they work. You can view all…

The importance of open-source hardware has been increasing in recent years with the introduction of the RISC-V Open ISA. This has also accelerated the push…

A Look At The ET-SoC-1, Esperanto’s Massively Multi-Core RISC-V Approach To AI | David Schor, WikiChip Fuse

A Look At The ET-SoC-1, Esperanto’s Massively Multi-Core RISC-V Approach To AI | David Schor, WikiChip FuseAsk ten different engineers how they would design an AI accelerator and you’ll get ten different ways to arrange the billions of transistors on a…

Huami Will Unveil Self-developed OS, Chip, GPU at Next Beat 2021 Conference | Kamlesh Bhati, Sparrows News

Huami Will Unveil Self-developed OS, Chip, GPU at Next Beat 2021 Conference | Kamlesh Bhati, Sparrows NewsThe well-known smart wearable device manufacturers Huami Technology previously announced that it will hold the Next Beat 2021 conference on July 13, the theme of…

Building occupancy management solution using the TensorFlow Object Detection API | GreenWaves Technologies

Building occupancy management solution using the TensorFlow Object Detection API | GreenWaves TechnologiesGreenWaves has developed a people counting solution for occupancy management in smart building systems, providing real-time insights into how available space is used by employees…

RISC-V Electronic Design Industry Predictions 2021 | EDACafe’

RISC-V Electronic Design Industry Predictions 2021 | EDACafe’The RISC-V era of computing is here. Today there are more commercial IP providers working on RISC-V than any other architecture. Adoption is growing quickly,…

Chinese Startups and Venture Capitalists Bet Big on Open Source RISC-V | China Money Network

Chinese Startups and Venture Capitalists Bet Big on Open Source RISC-V | China Money NetworkThe topic of semiconductors has constantly been in the headlines in 2020. In China, the need for establishing an "independent and controllable" domestic chip industry…

Axiomise joins RISC-V International | iCrowdNewswire

Axiomise joins RISC-V International | iCrowdNewswireLONDON, UK. –– 6 January 2021 –– Axiomise® joined RISC-V International, a non-profit, corporation driving the adoption of the open-specification RISC-V instruction set architecture. Axiomise has…

As we celebrate over 50 years of microprocessors, the industry has embraced every generation of silicon process technology with architectural innovation plus new design methods…

Swedish Cobham and Spanish fentISS deepen their relationship | ArchiTecnologia

Swedish Cobham and Spanish fentISS deepen their relationship | ArchiTecnologiaSwedish hardware developer Cobham Gaisler and Spanish software company fentISS collaborate to promote computing solutions. RISC-V continues unstoppable in Europe, the limit will be the stars, well said, because…

Yosys and Verilator. We strongly believe that the support is a necessary step in building a collaborative ecosystem and scalable and reproducible CIs, especially publicly accessible ones…

A look back at RISC-V Development Timeline in 2020 | SEEED Studio

A look back at RISC-V Development Timeline in 2020 | SEEED StudioCalista Redmond, CEO of RISC-V International, has mentioned that they ” saw an increased momentum of RISC-V cores, SoCs, developer boards, software and tools across…

Yosys and Verilator. We strongly believe that the support is a necessary step in building a collaborative ecosystem and scalable and reproducible CIs, especially publicly accessible ones…

2019 announcements, 2020 was promising to be an exciting year for Amlogic and Rockchip with the expected launch of RK3588 and S908X high-end processors for 8K capable devices, but we’ll…

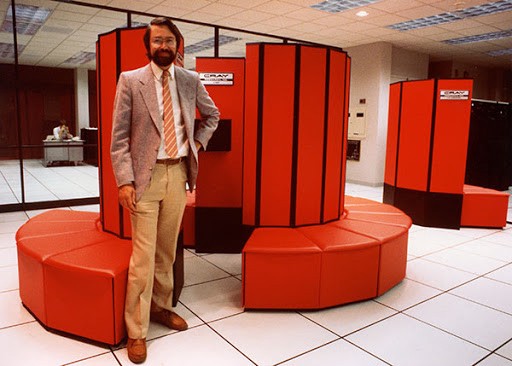

RISC-V Vector Instructions vs. ARM and x86 SIMD | Erik Engheim, Medium

RISC-V Vector Instructions vs. ARM and x86 SIMD | Erik Engheim, MediumIn the 1980s, super-computers looked like what you see in the image below. The semi-circular shape of a Cray was synonymous with super computers in the 80s.…