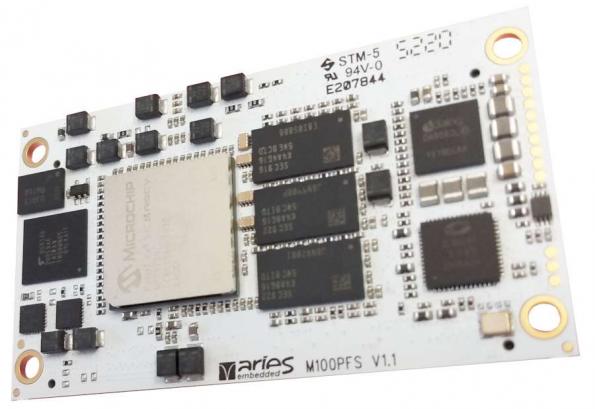

M100PFS SoM with Microchip’s PolarFire SoC FPGA Goes into Series Production

M100PFS SoM with Microchip’s PolarFire SoC FPGA Goes into Series ProductionARIES Embedded Expands System-on-Modules Product Range with First RISC-V Based FPGA Module Fuerstenfeldbruck, Germany, June 8, 2021 – ARIES Embedded, a specialist in embedded services…

As Linux Foundation’s Zephyr Project Turns Five, Addressing Constrained Device Challenges is More Important Than Ever | IoT Evolution, Arti Loftus

As Linux Foundation’s Zephyr Project Turns Five, Addressing Constrained Device Challenges is More Important Than Ever | IoT Evolution, Arti LoftusNoting nearly 1,000 contributors, 50,000 commits building advanced support for multiple architectures including ARC, Arm, Intel, Nios, RISC-V, SPARC and Tensilica, and more than 250…

RISC-V RV32I RTL Architecture | Maven Silicon

RISC-V RV32I RTL Architecture | Maven SiliconThis video explains the RTL architecture of an RV32I RISC-V processor. Also, it shows how we can create the RISC-V RTL using basic building blocks…

Alibaba Future-Proofing Cloud OS, Will Support Multiple Architectures | WebProNews, Matt Milano

Alibaba Future-Proofing Cloud OS, Will Support Multiple Architectures | WebProNews, Matt MilanoAlibaba is working to make its Apsara cloud OS compatible with a variety of architectures in an effort to future-proof it. Alibaba started as an…

The Zephyr Project Celebrates 5th Anniversary with new members and inaugural Zephyr Developer Summit on June 8-10

The Zephyr Project Celebrates 5th Anniversary with new members and inaugural Zephyr Developer Summit on June 8-10“RISC-V and Zephyr were both designed to drive innovation in the hardware space with open source technologies that are accessible to everyone,” said Mark Himelstein,…

Recently, Huawei released their first RISC-V development system to help engineers use the HarmonyOS operating system targeted at IoT devices. So why is Huawei looking…

Antmicro Open Source Portal launched

Antmicro Open Source Portal launchedAntmicro was founded on the belief that open source can dramatically accelerate technological progress by enabling collaboration, transparency and freedom to customize, improve and combine…

TII becomes a strategic member of the global organisation whose open-source standard allows for collaboration and breakthroughs in the computer chip industry, including the ability…

PUFsecurity and Andes Technology Cooperate to Integrate Crypto Coprocessor PUFiot into RISC-V AIoT Security Platform

PUFsecurity and Andes Technology Cooperate to Integrate Crypto Coprocessor PUFiot into RISC-V AIoT Security PlatformHsinchu Taiwan, June 02, 2021 (GLOBE NEWSWIRE) -- PUFsecurity, a security solutions IP company, and Andes Technology (TWSE: 6533), a leading RISC-V CPU IP vendor,…

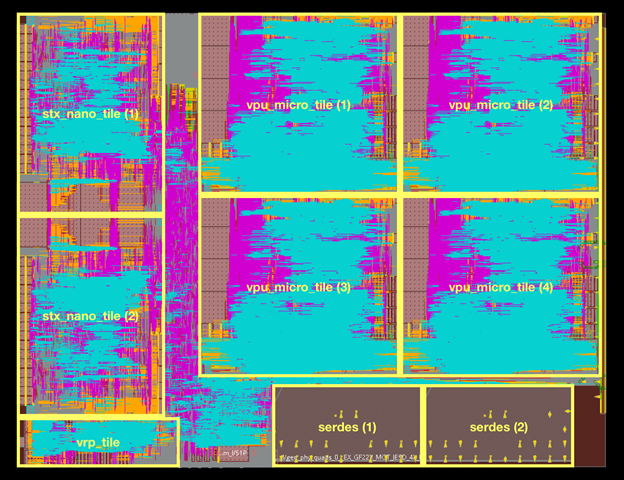

European supercomputer test chip tapes out | eeNews, Peter Clarke

European supercomputer test chip tapes out | eeNews, Peter ClarkeThe EPAC 1.0 test chip is now ready to be sent to fabrication, It contains a number of accelerator cores some based on RISC-V instruction…

#TII’s Secure Systems Research Centre (#SSRC) has become a strategic member of RISC-V International, an organisation which directs the future development and drives the adoption…

ABU DHABI, (UrduPoint / Pakistan Point News / WAM - 02nd Jun, 2021) Technology Innovation Institute (TII), the applied research pillar of Abu Dhabi’s Advanced…

What is RISC-V? Origins and Forecast | Tech Design

What is RISC-V? Origins and Forecast | Tech DesignRISC-V ISA delivers free, extensible software and hardware freedom on architecture, paving the way for years of computing design and innovation. Read the full article.]]>

Linux on RISC-V with Open Source Hardware (OSSummit Japan 2020) | Drew Fustini

Linux on RISC-V with Open Source Hardware (OSSummit Japan 2020) | Drew FustiniWant to run Linux on open hardware? This talk will explore how the RISC-V, an open instruction set (ISA), and open source FPGA tools can…

Semiconductor Engineering sat down to discuss security risks across multiple market segments with Helena Handschuh, security technologies fellow at Rambus; Mike Borza, principal security technologist for…

AdaCore Introduces GNAT Pro for the Wind River® Helix™ Virtualization Platform

AdaCore Introduces GNAT Pro for the Wind River® Helix™ Virtualization PlatformGNAT Pro Ada, C and C++ development toolsuites in support of the Wind River® Helix™ Virtualization Platform. Offered in separate Ada and C/C++ packages, GNAT Pro enhances Helix Platform's…

New methodologies are being developed to deal with increasing complexity. Debug is starting to be rethought and retooled as chips become more complex and more…

M1108 AI accelerator chip delivers up to 35 TOPS for high-end edge AI applications | Abhishek Jadhav, CNX Software

M1108 AI accelerator chip delivers up to 35 TOPS for high-end edge AI applications | Abhishek Jadhav, CNX SoftwareM1108 AI accelerator chip delivers up to 35 TOPS for high-end edge AI applications Last week, Mythic announced a breakthrough with compute-in-memory technology based on…

Pine64’s PINECIL RISC-V soldering iron launched for $25 | Jean-Luc Aufranc, CNX Software

Pine64’s PINECIL RISC-V soldering iron launched for $25 | Jean-Luc Aufranc, CNX SoftwarePINECIL RISC-V soldering iron during Pine64’s release of PineCube open-source IP camera development kit, and the good news is the soldering iron is now available…

New methodologies are being developed to deal with increasing complexity. Debug is starting to be rethought and retooled as chips become more complex and more…

already available. As usual, the new release introduces a range of features, modifications and fixes, enabling developers to design complex embedded IoT systems more effectively…