Google Summer of Code’21 at FOSSI Foundation: M-extension Support for SERV | Zeeshan Rafique, RISC-V Ambassador

Google Summer of Code’21 at FOSSI Foundation: M-extension Support for SERV | Zeeshan Rafique, RISC-V AmbassadorThis project aims to design and integrate the integer “Multiplication and Division Unit (MDU)” with SERV core as a co-processor. The MDU will support all…

RISC-V RV32I R-Type | Maven Silicon

RISC-V RV32I R-Type | Maven SiliconThis video explains the RV32I R-Type instructions. RISC-V is growing rapidly, follow this RISC-V video blog series to obtain knowledge about RISC-V processors, Instruction formats,…

The RISC-V Zfinx Task Group is thrilled to announce the Zfinx extension (pronounced “z-f-in-x”) has entered the public review period. The Zfinx extension brings the…

StarFive open source single board hardware platform will be officially released by the end of Q3 2021

StarFive open source single board hardware platform will be officially released by the end of Q3 2021At Starfive Technology, we have been committed to promoting the development of the global RISC-V open source software and hardware ecosystem since we were founded.…

The seL4 Foundation and RISC-V International are pleased to announce that Ryan Barry from UNSW Sydney has completed the proof that the seL4 microkernel on…

“中国信芯” 再迈一步,万向区块链携生态伙伴举办RISC-V区块链行业工作组首次公开活动

“中国信芯” 再迈一步,万向区块链携生态伙伴举办RISC-V区块链行业工作组首次公开活动(点击这里查看原文)由上海科技大学和中国科学院软件研究所联合主办,中国RISC-V产业联盟(CRVIC)、中国开放指令生态联盟(CRVA)、CNRV社区协办的第一届「RISC-V中国峰会」于日前盛大开幕。6月24日,万向区块链作为RISC-V 区块链行业工作组(Blockchain SIG)的发起单位,携手上下游生态企业在上海科技大学(张江校区)举办“区块链+RISC-V”专场论坛及研讨会。 RISC-V区块链行业工作组于今年2月由万向区块链携手摩联科技、跃昉科技、赛昉科技、SiFive共同发起成立,致力于通过研究探索芯片和区块链技术的整合构筑“中国信芯”(Chinese TEA),着力打造可信嵌入式架构(TEA),构建一个人人都可以参与的开放平台。 本次峰会同期的“区块链+RISC-V”专场论坛和研讨会是RISC-V区块链行业工作组成立以来举办的首个公开活动,也是区块链行业工作组经过几个月的探索,首次面向所有技术人员与爱好者的一次汇报。在上午的专场论坛中,万向区块链执行总裁王允臻、跃昉科技首席技术官江朝晖、摩联科技创始人兼首席执行官林瑶应邀作为演讲嘉宾分享了区块链技术在物联网领域的最新成果及应用案例。 万向区块链执行总裁王允臻 万向区块链执行总裁王允臻在演讲中提到:“RISC-V和区块链作为两大开源技术,是打造可信开源系统的硬件和软件基石。因此,我们非常积极地在RISC-V基金会上促进跨技术领域、跨行业的架构集成,充分发挥RISC-V这种开源芯片架构自带的公平、公正、开放、透明、安全和隐私的能力。”万向区块链通过积极投入物联网与区块链的创新融合,提升数据源可信性,并以数据一键上链提供操作的便捷。万向区块链携手生态合作伙伴成立的RISC-V区块链行业工作组致力于标准制定、技术创新、生态共赢,提升开创性的芯片架构竞争力,打开全新应用场景。 跃昉科技首席技术官江朝晖 未来,工业、物流、能源将成为物联网主要应用的行业,也是对安全要求最高的行业。目前,物联网的痛点在于架构终端设备多,数据可信程度低。“芯片方面首先需要解决的是芯片的安全问题。”跃昉科技首席技术官江朝晖分享道。同时,她也在为现场观众介绍芯片安全重要性的同时提到跃昉赋予每个芯片一个独特的ID,通过芯片+区块链确定数据来源的可信性。 摩联科技创始人兼首席执行官林瑶 “BoAT就像一艘船,帮助传统物联网企业把物理世界的有价值的数据,可信地运到区块链世界的新大陆。”摩联科技创始人兼首席执行官林瑶在论坛现场宣布了BoAT区块链应用框架正式推出面向RISC-V开放架构的开源版本——BoAT-V,其在加速推动物联网设备区块链赋能方面具有明显优势。摩联科技将与RISC-V生态中的合作伙伴一起不断优化围绕数据价值开放、实现开源生态的商业系统,共同打造物联网可信数字底座。 “中国信芯”的发展,需要区块链企业与生态企业的共同参与。下午的“区块链+RISC-V”主题研讨会邀请了行业专家从区块链、芯片厂商、模组厂商、运营商、平台服务商等角度,分享RISC-V+物联网+区块链的技术创新和商业落地案例。 万向区块链“区块链+”技术部高级总监屠文慧从区块链的定义出发,介绍了区块链的发展进程与挑战,分享了万向区块链的落地应用案例。自2020年提出分布式认知工业互联网,万向区块链用技术赋能新能源电池、肉牛养殖、石油化工等传统行业与场景,构筑区块链生态链盟,打通产业协同,同时以万向区块链数字城市解决方案为缩影,绘制了区块链+RISC-V赋能未来数字社会的蓝图。 同时,屠文慧作为RISC-V区块链行业工作组首任主席也向芯片、物联网、区块链等相关行业的伙伴们发出了诚挚邀请,欢迎大家点击下方链接,访问工作组官网,申请加入! 点击链接,加入RISC-V区块链行业工作组: https://lists.riscv.org/g/tech-blockchain 中国信息通信研究院泰尔终端实验室信息安全部副主任国炜通过介绍冷链物流行业规范、物联网安全分级认证,分析《关于加快推动区块链技术应用和产业发展的指导意见》表达了对区块链技术应用和产业发展持乐观态度。 中移物联网有限公司集成电路创新中心总经理肖青、千寻位置网络有限公司终端事业部总经理郦可、上海赛昉科技有限公司软件副总Frank、摩联科技联合创始人&CTO许刚分别结合企业特色,从芯片技术和软件系统角度介绍了区块链+RISC-V在不同行业中的机遇与挑战。 由摩联科技联合创始人&CTO许刚主持的生态圆桌讨论邀请到中国信息通信研究院泰尔终端实验室信息安全部副主任国炜、长虹信息安全首席科学家唐博、华登国际副总裁刘锋作为圆桌嘉宾,就“如何更好地支持物联网+区块链的发展”、“从安全的角度来看是开源还是闭源会更安全”等话题进行了讨论。 产业生态的健全离不开政府政策法规的指导和认证标准的规范,同时也需要更多产业主体在技术层面及产品层面的共同努力。区块链是一种分布式商业模式创新,以区块链为设计思路构建的分布式物联网系统是在商业上、技术上形成闭环的。在开源生态上打造分布式商业的逻辑是出于战略上和商业策略的选择,无论开源或闭源,其代码安全都是相对的,即使是完全公开的开源代码也只是攻防博弈,在交锋中促进技术的发展。区块链+RISC-V产业命运共同体需要所有生态体系内的合作伙伴携手共进,共同构筑可信的数字世界。 上海赛昉科技有限公司软件事业部副总Frank、千寻位置网络有限公司终端事业部总经理郦可先生、紫光展锐工业电子产品规划总监李占博先生、芯翼信息科技董事长&CEO肖建宏在由凯捷科技研发中国区半导体事业部总监石贤帅主持的区块链+芯片圆桌讨论中就 “区块链对芯片发展的重要性”、“链对芯片设计在物联网区块方面面临的挑战”、“区块链对物联网商业模式的影响。”、“开源会给芯片行业带来的变化”等话题各抒己见,共谋发展。 物联网除了链上安全外,还要考虑上链安全,达到全链上任何一点都可信。区块链在芯片里有定制的可信区域,从硬件上进一步保证了数据可信。区块链技术重构了利益获取,在区块链的世界里很难区分出来谁是甲方谁是乙方,这是典型的交易方式的变化。过去没有一种很好的商业模式保证自己开源了就能够有确定性的收益,如今在开源基础上又有了区块链技术,更开放更包容是历史发展的必然趋势。中国最大的优势是有非常集中化的体制可以试验很多东西,智慧城市、物联网的发展、基础设施走在世界的前沿,在此基础上有大量的东西可以让我们实验,带来技术的突飞猛。未来不是我们能想象的,我们所能做的是拼命跑以期跟上时代的发展,走在科技的前沿。 “中国信芯”的打造需要天马行空的想象,也需要脚踏实地的研发。以行业数字化需求为出发点,融合RISC-V的芯片架构优势及区块链的信任机制,推动国内乃至全球区块链技术与物联网的有机结合与落地应用。万向区块链基于PlatONE联盟链,联合矩阵元打造的PlatONE+BoAT物联网赋能平台,将区块链与物联网有机地融合在一起,为各行业的数字化转型升级提供了“可信数字底座”。 未来,万向区块链会持续与生态合作伙伴探索“中国信芯”的进一步发展和落地,并将融合创新的解决方案在分布式认知工业互联网、数字城市、资产数字化等重点领域布局。 由万向区块链实验室主办的“2021上海区块链国际周”,计划于9月10日至15日登陆上海虹口。作为备受瞩目的全球知名区块链活动之一,今年的国际周将一如既往地以多样化的形式为观众呈现富于行业洞见的深度内容,聚集这一年的热点人物与话题,再度激荡风云,奏响行业时代之音。 本届区块链国际周由黑客马拉松、开放日、第七届区块链全球峰会三部分组成。

The 2021 RISC-V Summit Will Demonstrate Adoptions and Technical Advances This December in San Francisco

The 2021 RISC-V Summit Will Demonstrate Adoptions and Technical Advances This December in San FranciscoZURICH and SAN FRANCISCO – July 28, 2021 – RISC-V International announced the 2021 RISC-V Summit that will bring together the open hardware community for…

Life in a Formal Verification Lane | Shivani Shah

Life in a Formal Verification Lane | Shivani ShahThis summer, I got the opportunity to work as a Formal Verification Intern with Axiomise for six weeks. I’m a keen designer and love working…

What You Need to Know About Verilator Open Source Tooling | Rob Mains, CHIPS Alliance

What You Need to Know About Verilator Open Source Tooling | Rob Mains, CHIPS AllianceVerilator is a high performance, open source functional simulator that has gained tremendous popularity in its usage and adoption in the verification of chip design.…

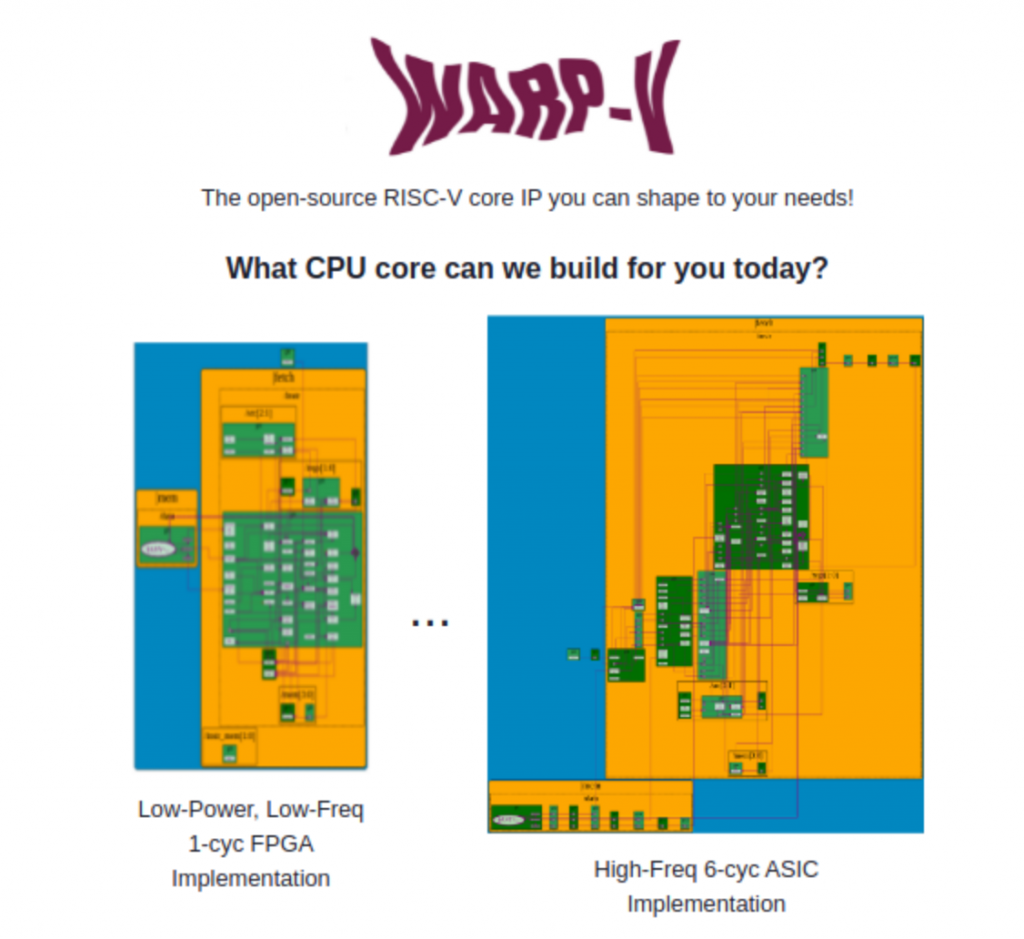

A Free RISC-V CPU Core Builder – Democratizing CPUs | Steve Hoover, Redwood EDA

A Free RISC-V CPU Core Builder – Democratizing CPUs | Steve Hoover, Redwood EDAThere are now over a hundred RISC-V CPU cores listed in the RISC-V Exchange! Amazing. If you need a RISC-V CPU core, you’ll likely be…

RISC-V RV32I Assembly – Multiplication | Maven Silicon

RISC-V RV32I Assembly – Multiplication | Maven SiliconThis video shows how we can implement the Multiplication using add and shift RV32I instructions. RISC-V is growing rapidly, follow this RISC-V video blog series…

It’s no secret that the past twenty years has seen remarkable progress in technology innovation. Smartphones opened up a whole new ecosystem of applications and…