Advanced RISC-V Training Course | Maven Silicon – RISC-V Global Training Partner

Advanced RISC-V Training Course | Maven Silicon – RISC-V Global Training PartnerBy Sivakumar P R In this video, our Founder and CEO, Mr. P R Sivakumar, explains how he has authored the new RISC-V training course…

Message from RISC-V International 2024 is now well underway and we have some exciting new developments from our members worldwide! RISC-V is truly a global…

Introducing the RISC-V Enterprise Software Ecosystem Dashboard

Introducing the RISC-V Enterprise Software Ecosystem DashboardAuthor: Isaac Chute, Director of Software Ecosystem, RISC-V International Historically there have been many iterations of compute platforms, such as Alpha, Vax, Solaris, PA-RISC, x86,…

DUBLIN, March 14, 2024 /PRNewswire/ -- The "Automotive RISC-V Chip Industry Research Report, 2024" report has been added to ResearchAndMarkets.com's offering. Read the full release.

Securing software execution with CHERI on a Codasip A730 RISC-V core

Securing software execution with CHERI on a Codasip A730 RISC-V coreAuthor: Roddy Urquhart, Sr Technical Marketing Director, Codasip Introducing CHERI With cyber-attacks on systems growing in frequency and sophistication it is essential to improve the…

Securing your vehicle used to mean remembering to lock your doors at night and hiding your belongings under the seat when parked in public lots.…

SHANGHAI--(BUSINESS WIRE)--VeriSilicon (688521.SH) today announced the integration of its Image Signal Processor (ISP) IP ISP8000, DeWarp Processor IP DW200, and 2.5D Graphics Processor Unit (GPU)…

SANTA CLARA, Calif., March 13, 2024 /PRNewswire/ --Tenstorrent and MosChip Technologies announced today that they are partnering on design for Tenstorrent's cutting-edge RISC-V solutions. In selecting MosChip…

embedded world 2024: Codasip demonstrates CHERI memory protection

embedded world 2024: Codasip demonstrates CHERI memory protectionMunich, Germany, 13 March 2024 –Codasip, the leader in RISC-V Custom Compute, will demonstrate CHERI memory protection and HW/SW co-optimization at next month’s embedded world…

People to Watch 2024 – Calista Redmond

People to Watch 2024 – Calista RedmondCongratulations on your selection as a 2024 HPCwire Person to Watch. As a longtime electronics industry executive and the former president of the member-driven OpenPOWER…

【Mar. 12, 2024 -Hsinchu, Taiwan】Andes Technology (TWSE: 6533), since the first agreement signed with National Chiao Tung University in 2010, has actively keeping engaged in…

What is RISC-V and Why Has it Become Important for Java?

What is RISC-V and Why Has it Become Important for Java?RISC stands for reduced instruction set computer, and V points to its fifth release in 2015. RISC-V is the new processor architecture to watch out for.…

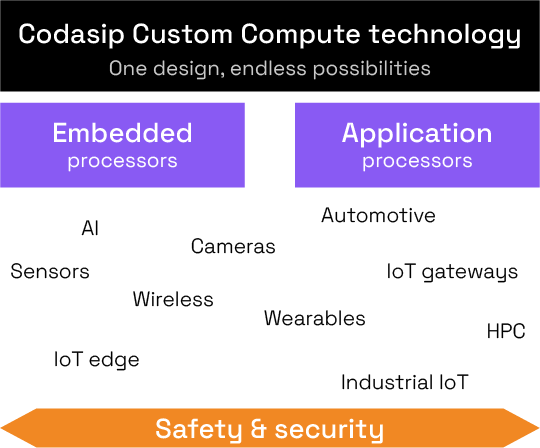

Codasip announces next-generation RISC-V processor family for Custom Compute

Codasip announces next-generation RISC-V processor family for Custom ComputeIntroducing the highly flexible 700 family for unlimited innovation Munich, Germany, 17 October 2023 – Codasip, the leader in RISC-V Custom Compute, announced today a…

Research Consortium sets Standards in the Field of Open Source Hardware: Open Tools used for a Security Chip

Research Consortium sets Standards in the Field of Open Source Hardware: Open Tools used for a Security ChipThe security chip (at the middle of the bottom) is built in flip-chip technology on an auxiliary board and plugged into a standard socket on…

What is RISC-V and how will it redefine your next-gen wearable tech?

What is RISC-V and how will it redefine your next-gen wearable tech?When discussing computer hardware, x86, and ARM are household names when discussing microprocessor architecture. They've been around for decades and are still going strong, powering…

Hsinchu, Taiwan – Oct. 17, 2023 – Andes Technology, the renowned supplier of high-efficiency, low-power 32/64-bit RISC-V processor cores and a Founding Premier member of RISC-V…

Qualcomm to Bring RISC-V Based Wearable Platform to Wear OS by Google

Qualcomm to Bring RISC-V Based Wearable Platform to Wear OS by GoogleHighlights: Qualcomm and Google are extending their collaboration on wearables by developing a RISC-V Snapdragon Wear™ platform that will power next-generation Wear OS solutions. Work…

Qualcomm Adopts RISC-V for Next-Gen Snapdragon Wear Platform

Qualcomm Adopts RISC-V for Next-Gen Snapdragon Wear PlatformQualcomm and Google announced that they had agreed to expand their partnership to development of a Snapdragon Wear platform based on the RISC-V instruction set…

SharpRISCV Overview: A Browser-Based RISC-V Assembler for Seamless Learning and Exploration

SharpRISCV Overview: A Browser-Based RISC-V Assembler for Seamless Learning and ExplorationIn the ever-evolving landscape of computer architecture, RISC-V stands out as an open-source instruction set architecture that offers flexibility and adaptability. To facilitate learning and…

Codasip announces next-generation RISC-V processor family for Custom Compute

Codasip announces next-generation RISC-V processor family for Custom ComputeMunich, Germany -- October 17, 2023 – Codasip®, the leader in RISC-V Custom Compute, announced today a new highly configurable family of RISC-V baseline processors for…

Codasip 700 RISC-V processor family: Bringing the world of Custom Compute to everyone

Codasip 700 RISC-V processor family: Bringing the world of Custom Compute to everyoneToday, technology innovators must have new ways to create differentiated products. How are they supposed to meet the demand for more computational performance when semiconductor scaling…

SiFive Rolls Out RISC-V Cores Aimed at Generative AI and ML

SiFive Rolls Out RISC-V Cores Aimed at Generative AI and MLSiFive has released two new processors, one to target machine learning applications, and one to target general-purpose HPC. The RISC-V movement is one of the…

SiFive unveils two new high-performance RISC-V processors

SiFive unveils two new high-performance RISC-V processorsSiFive, a RISC-V processor design firm, unveiled two new chip designs aimed at bringing a high-performance computing solution to various industries. The announcement of the…

SiFive Announces Differentiated Solutions for Generative AI and ML Applications Leading RISC-V into a New Era of High-Performance Innovation

SiFive Announces Differentiated Solutions for Generative AI and ML Applications Leading RISC-V into a New Era of High-Performance InnovationSanta Clara, Calif., Oct. 11, 2023 –SiFive, Inc., the pioneer and leader of RISC-V computing today announced two new products designed to address new requirements for…